Warning:以下是王富贵同学以及小组成员的总体设计,需要源文件可私信寻求帮助,下文所有内容如有侵权请联系我删除。

设计意义:综合运用电子技术(模拟电子线路,数字电子线路)课程所学知识,设计、安装、调试具体的电子线路(不使用单片机、ARM和FPGA等),并写出电路系统设计报告。初步了解工程设计实践的一般过程和步骤,初步掌握其一般技能

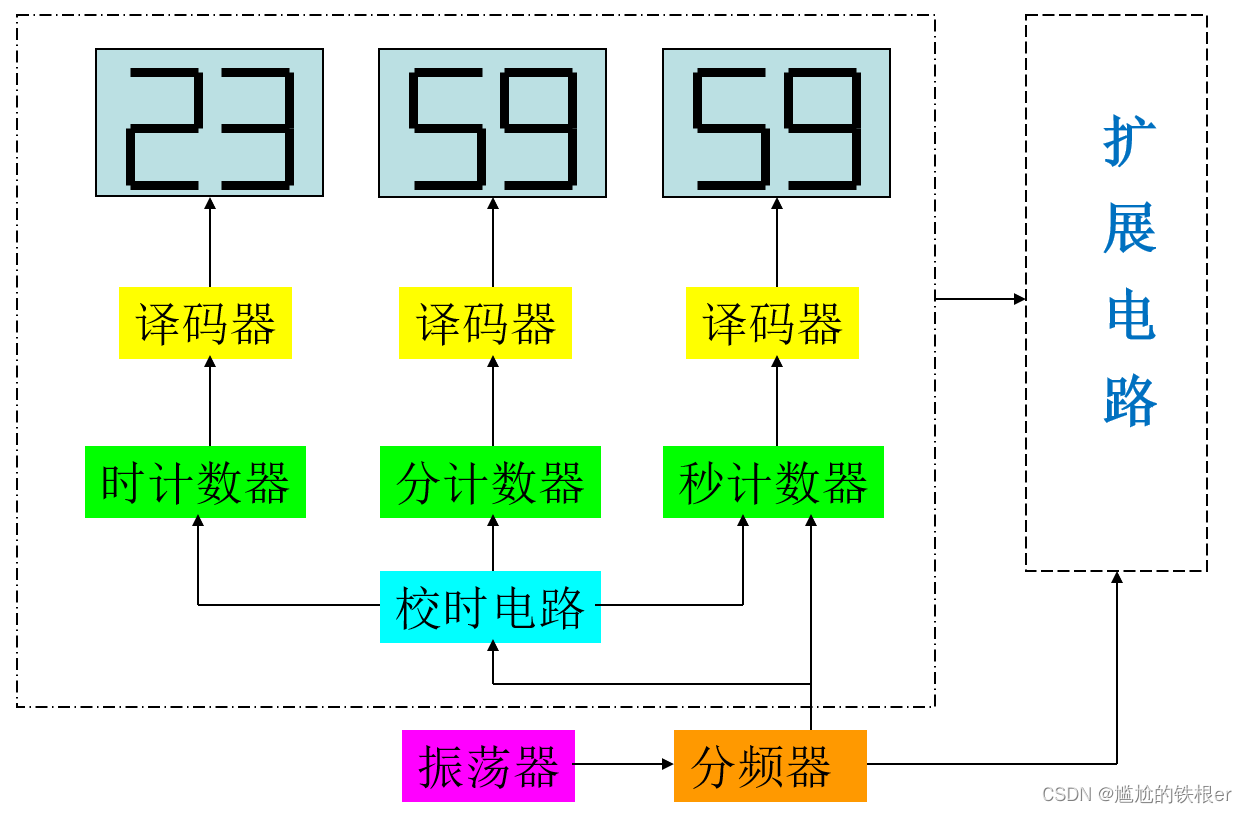

设计要求:能够准确计时;具有时、分、秒数字显示: 23时59分59秒形式;具有校时功能;(拓展功能:闹钟系统;整点报时)

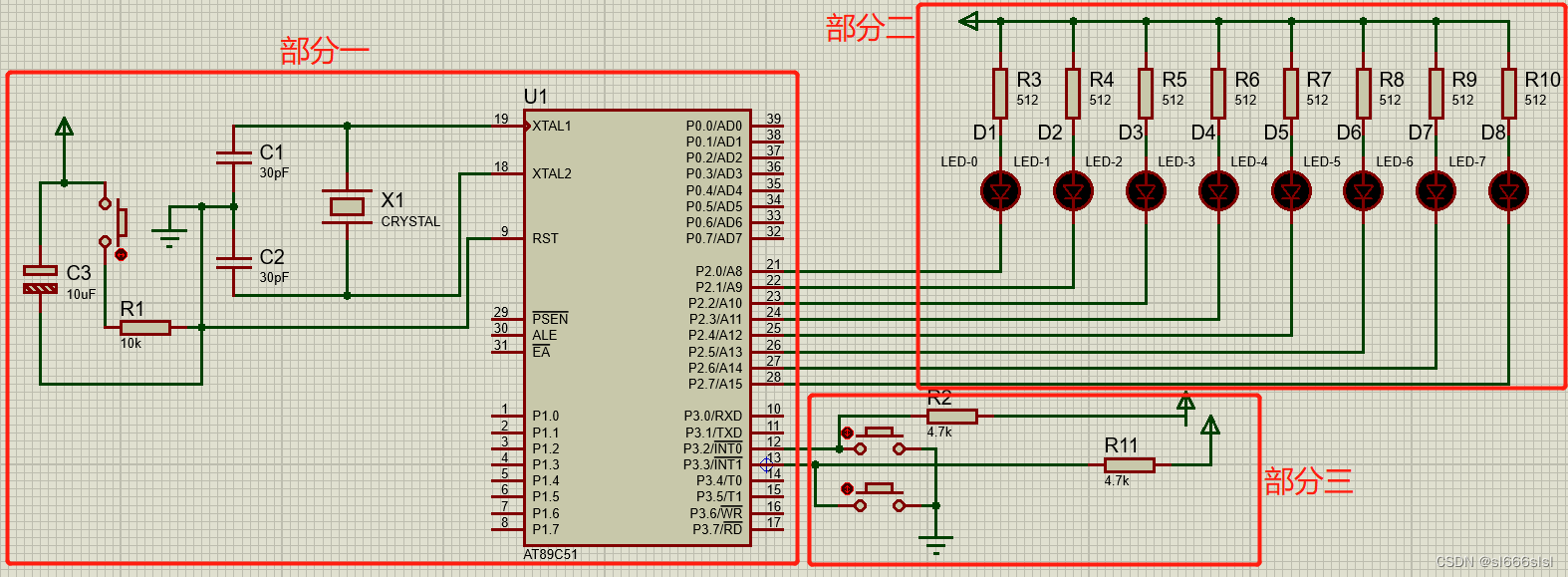

数字式时钟电路设计框图

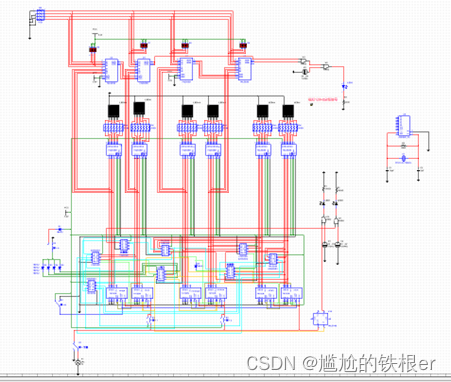

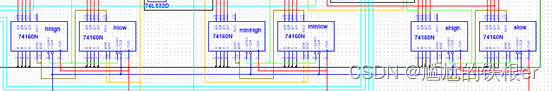

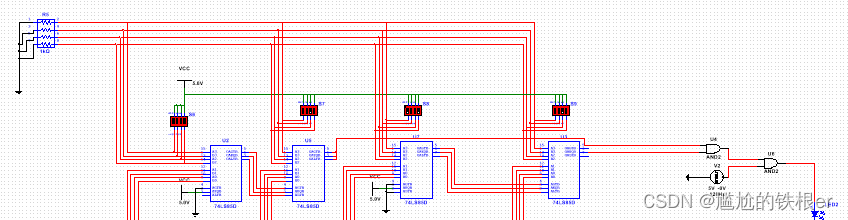

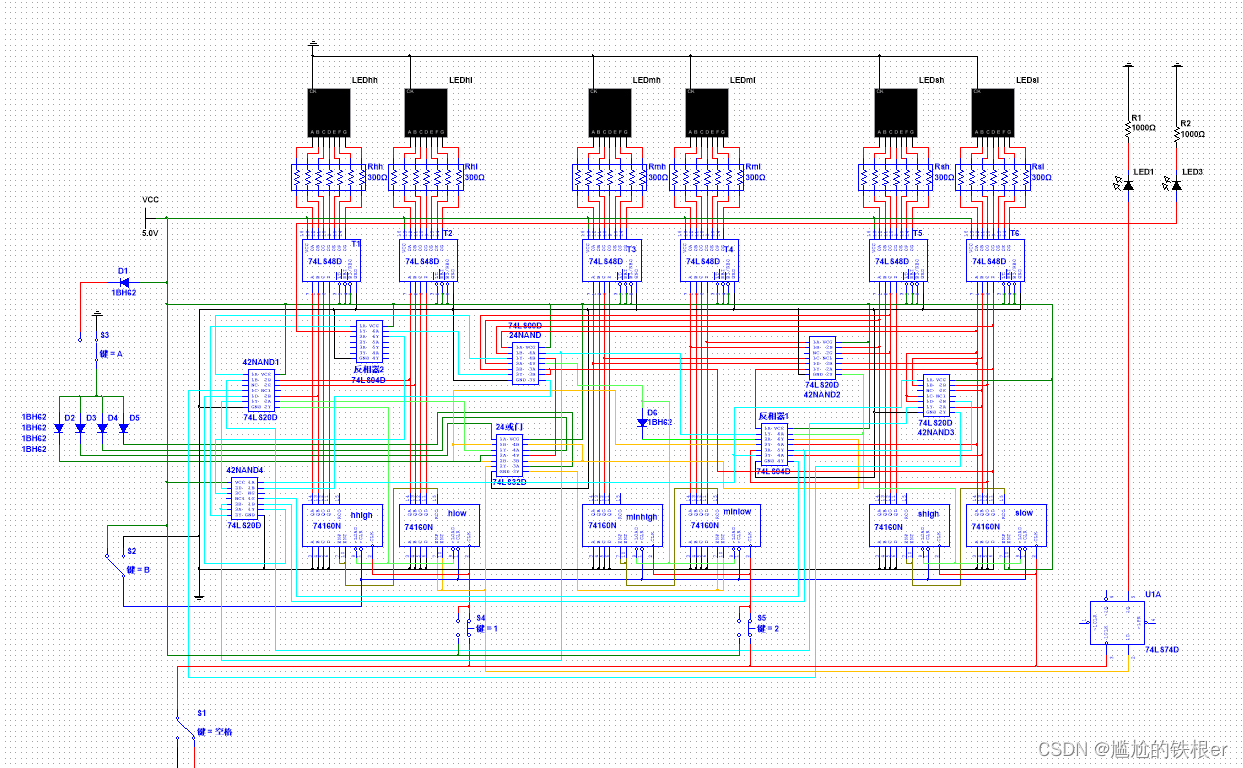

本次设计以模块化拼接为导向,充分调用已有器件,争取达到同步多功能、低能耗、简介布局的设计理念,依照老师做给出的整体框图搭建电路整体,Multisim仿真全局图(芯片化)(分频器位于右侧孤立部分暂未合并)如下:

模块陈述

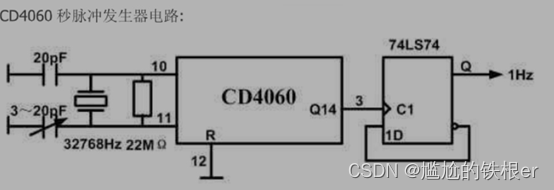

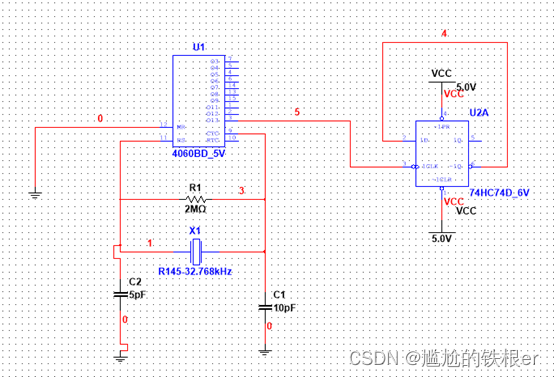

1.晶体震荡合并分频电路:

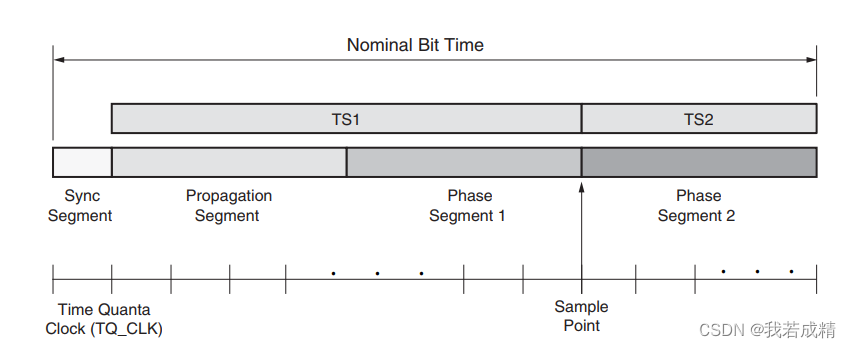

晶体振荡器电路给数字钟提供一个频率稳定准确的32768Hz的方波信号,可保证数字钟的走时准确及稳定。在这里需要的是1Hz计数方波信号,以及500(512)Hz、1000(1024)Hz的闹钟(报时)供给电路。

在这里应用CD4060分频器在32768Hz中分出所需三个频率,由于分频器为14级2分频,最多达到极限值2Hz,所以还需要加入一个2分频电路得到1Hz时钟计数方波。

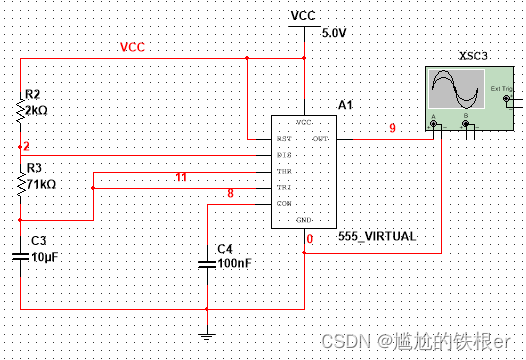

其实也可以用555定时器实现这个脉冲功能,只不过有些不稳定

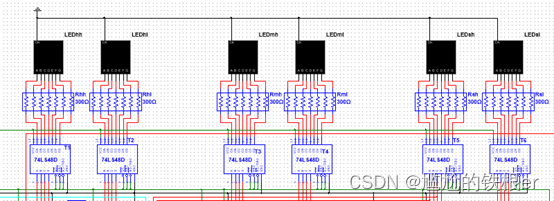

2.译码驱动及显示单元电路:

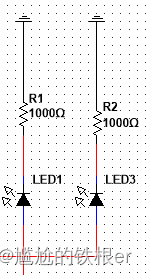

选择74LS47作为显示译码电路,选择共阴极LED数码管作为显示单元电路。由74LS47把输进来的二进制信号翻译成十进制数字,再由数码管显示出来。计数器实现了对时间的累计并以8421BCD码的形式输送到74LS47芯片,再由74LS47芯片把BCD码转变为十进制数码送到数码管中显示出来。下图所示为译码驱动及显示单元,从左至右依次为时分秒(十位/个位),由于仿真原因,特加入排阻300欧姆,使得仿真通过。

3.计时电路:

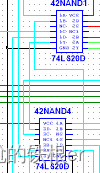

整体采用要求的十进制计数器74LS160芯片,实现同步计数排除冒险。下图从左至右依次为时分秒(十位/个位),通过load置数法(0000)拼接两片十进制芯片,分别实现(24时/60分、秒)进制。级间进位由一致load置位取反给出进位信号。具体反相器74LS04、4-2与非门74LS20、2-4与非门74LS20不再给出局部截图。

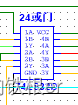

4.校时电路:

校时电路的灵魂就是通过按钮实现/代替实现计数脉冲,通过4-2或门74LS32 来实现与正常时钟进位同等效力。实际使用时,因为电路开关存在抖动问题,我们设计了一校时、置零使能,较为取巧的解决了抖动问题,使得抖动仅限制在手动脉冲当中。图为校时使能A、置零位B,图中二极管均为缓冲器。图为时校位1、分校位2(秒校位在各大时钟当中均不存在,且平时校时时根本无需调秒,故不设置,仅需要置零一下即可)

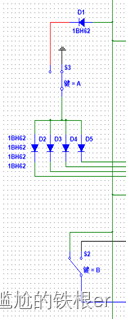

5.拓展功能整点报时电路:

在仿真中蜂鸣器暂时以发光二极管代替(图1),蜂鸣电路的设计灵魂就是取出x时59分50秒到x+1时00分00秒中间的50s、53s、56s、59s四个预备报时脉冲(500Hz)以及00整点报时脉冲(1000Hz),然后统一经由与非门判断输出信号通往蜂鸣器。在这里用4-2与非门74LS20实现该功能(图2)。

6.拓展功能闹钟定时电路:

闹钟定时的核心就是当前时间与预设时间的比较,但是闹钟较为困难的是和计数、校时电路协调设计,意思是通过校时按钮1、2输入时间再交由寄存器寄存并时刻同步比较,这样实在是非常困难,所以我们的设计理念就是硬件比较。利用四位二进制比较器74LS85进行预设值(开关设定)与具体时刻值进行对比。

(注:该图不是本人的直接版权,是本人的好朋友、小组成员的设计图)

附件:下图为不带有闹钟功能的所有电路(因闹钟部分完全模块化,与主电路仅有BCD总线上的联系,故可以分开展示)

文章来源:https://uudwc.com/A/3ZnD

文章来源:https://uudwc.com/A/3ZnD

以上是王富贵同学小组成员的总体设计,需要源文件可私信寻求帮助,上文所有内容如有侵权请联系我删除。文章来源地址https://uudwc.com/A/3ZnD