针对设计过程中的问题,如有疑问,欢迎留言评论!点我返回目录

1 简介

RS485通信属于串口通信中的半双工通信,RS485具有支持多节点(32个节点)、传输距离远(最大1219m)、接收灵敏度高(200mV电压)、连接简单(在构成通信网络时,仅需要一对双绞线作传输线)、能抑制共模干扰(差分传输)、成本低廉等特点,最高的传输速率可达10Mbps。在多站、远距离通信等多种工控环境中获得了广泛应用。

RS485的电平标准如下:

| 电平逻辑 | 逻辑1 | 逻辑0 |

| RS485 | +(2~6)V | -(2~6)V |

当接收端 AB间的电压差:

- 大于+200mv:高电平1。

- 小于-200mv:低电平0。

注意:其中逻辑1为B>A的状态,定义逻辑0为A>B的状态,AB之间的电压差的绝对值不小于200mv。

2 硬件电路设计

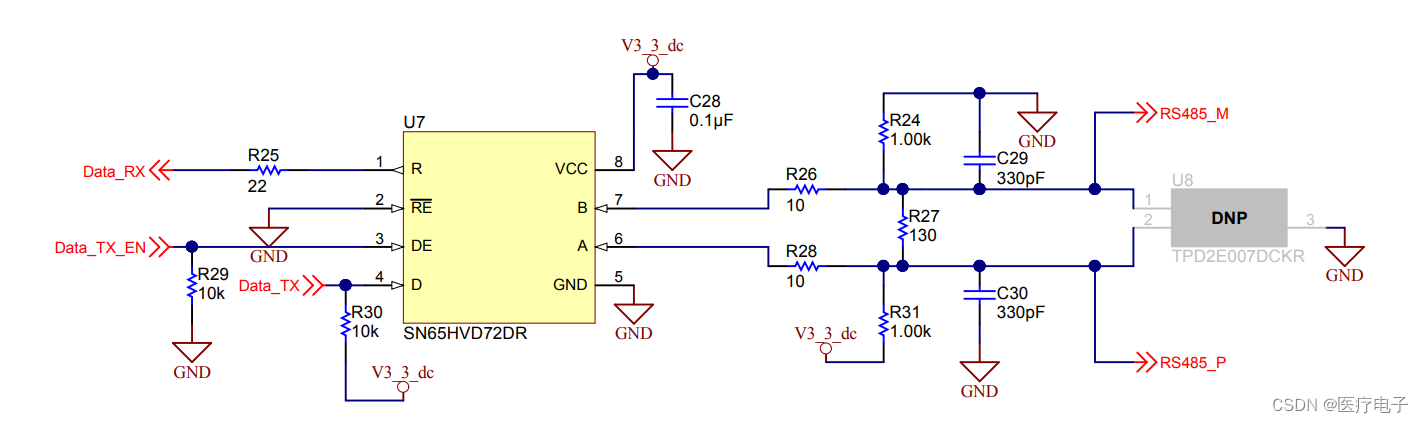

此处我们以SN65HVD72DR为例:

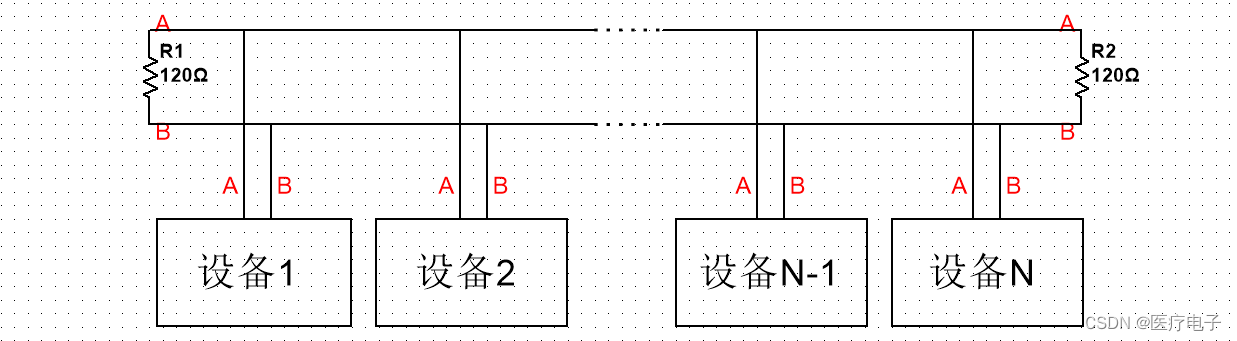

- 终端匹配电阻为一般为120Ω,此处为130Ω(具体阻值大小与应用场景有关,不清楚可直接按照120欧姆设计)

- B总线下拉至GND,A总线上拉至3.3V,是为了防止|A-B|≥200mV。

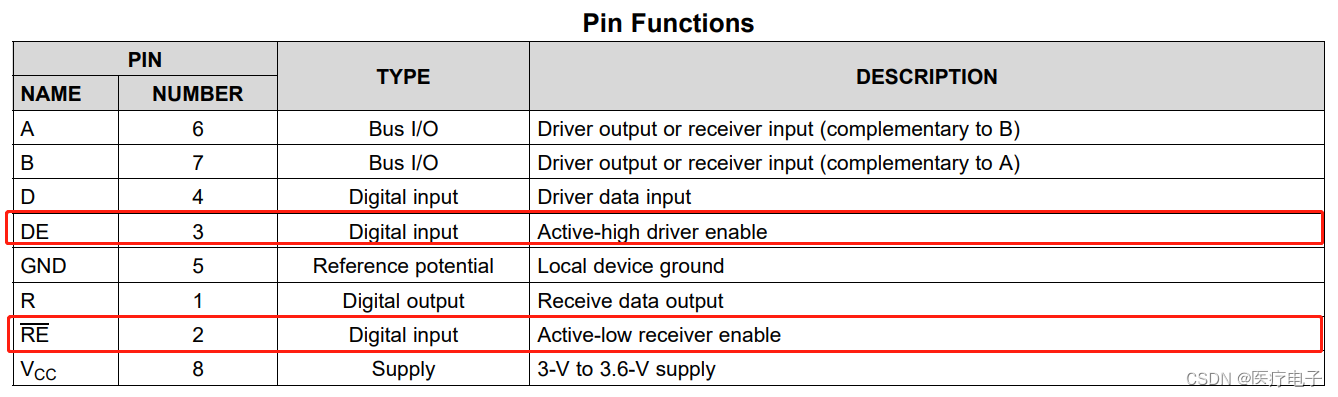

- DE与RE的功能:

- RE为低时,接受使能。

- DE为高时,发送使能。

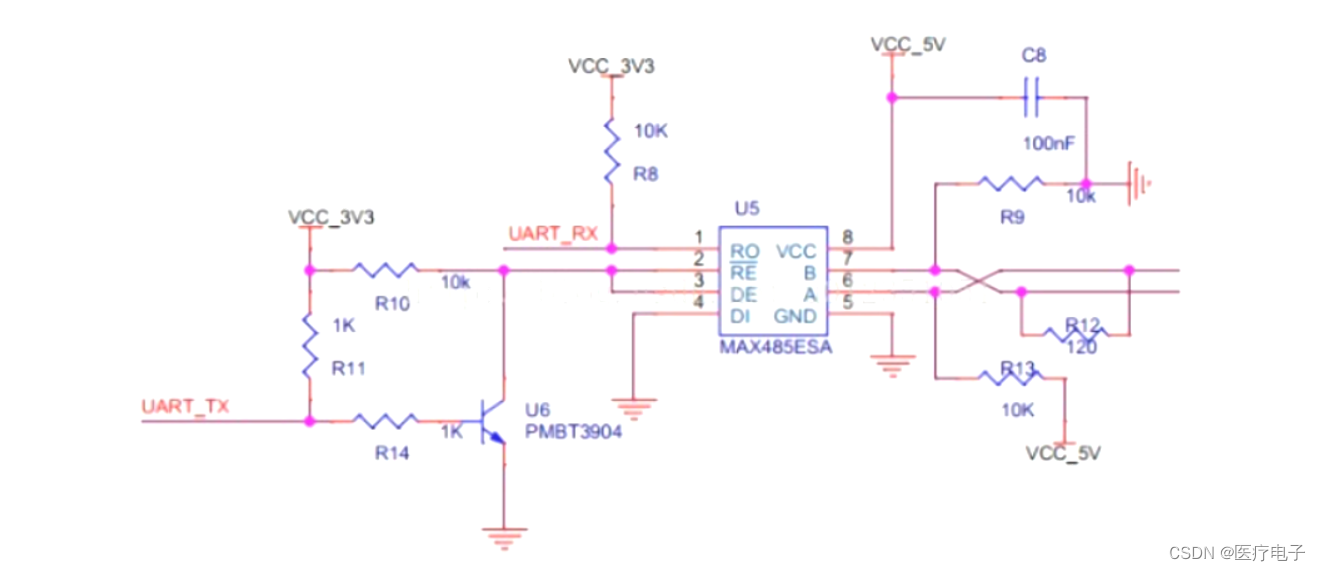

3 自动收发电路

鉴于切换接受和发送两种状态比较繁琐,此处介绍一种自动控制接收和发送的电路,具体电路如下:

- 接收:TX为高电平,三极管导通,RE为低电平使能,RO收数据有效,MAX485为接收态。

- 发送:发送数据1时,TX为高电平时,三极管导通,DE为低电平,此时收发器处于接收状态,驱动器就变成了高阻态,也就是发送端与A\B断开了,此时A\B之间的电压就取决于A\B的上下拉电阻了,A为高电平、B为低电平,也就成为了逻辑1了。

文章来源地址https://uudwc.com/A/3mZ9n

文章来源:https://uudwc.com/A/3mZ9n