名称:简易计时闹钟(代码在文末付费下载)

软件:ISE

语言:Verilog

要求:

简易计时闹钟:有四位数码管,前两位计分钟,表示00~99分钟,后面两位记秒,值为00~59秒。有三个按键,第一个是分键,第二个是秒键,第三个是启动/暂停键。功能:分秒两键同时按下清零且停止计时,外于设置态,按一次分键分钟加1, 99增1变为0;按一次秒键秒增1,59增1变为0。此状态下按启动/暂停键开始计时,设置值为0000则为正计时,设置值为非零值则为倒计时。

正计时时,按启动/暂停键会暂停计时,再按启动/暂停键则会继续计时。倒计时时,减到零时停止减数且发出警示蜂鸣声,直到启动/暂停键被按下时进入设置态且同时显示前设置值和停止发出蜂鸣声。

代码下载:简易计时闹钟ISE_Verilog/VHDL资源下载

代码网:hdlcode.com

设计文档(文档点击可下载):

1. 工程文件

2. 程序文件

3. 程序编译

4. Testbench

5. 仿真图

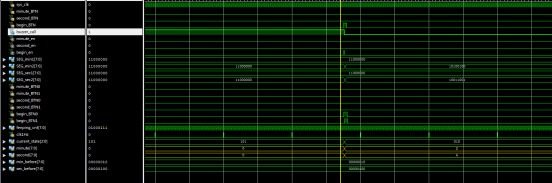

整体仿真图

正计时

暂停

暂停后重启

分秒同时按下,设置时间2分4秒,开始倒计时

倒计时结束蜂鸣器buzzer_call拉高

再按下启动键,进入设置态且同时显示前设置值和停止发出蜂鸣声

顶层端口文章来源:https://uudwc.com/A/9dn03

//简易计时闹钟 module time_count( sys_clk,//系统时钟100Hz minute_BTN,//分按键 second_BTN,//秒按键 begin_BTN,//启动按键 SEG_min1,//分钟十位 SEG_min2,//分钟个位 SEG_sec1,//秒钟十位 SEG_sec2,//秒钟个位 buzzer_call//蜂鸣器 ); input sys_clk;//系统时钟100Hz input minute_BTN;//分按键 input second_BTN;//秒按键 input begin_BTN;//启动按键 output reg [7:0] SEG_min1;//分钟十位 output reg [7:0] SEG_min2;//分钟个位 output reg [7:0] SEG_sec1;//秒钟十位 output reg [7:0] SEG_sec2;//秒钟个位 output buzzer_call;//蜂鸣器

文章来源地址https://uudwc.com/A/9dn03