PCB设计流程

设计准备工作(设计原理图、规划项目时间)→确认原理图→新建封装(添加封装及同步)→布局工作(设置好结构、开始布局,接口、模块化)→布线工作→优化及DRC→设计资料输出→打板测试

原理图

批量添加封装

原理图中Tools→Footprint Manager

同步网表

D+U, update to PCB

PCB

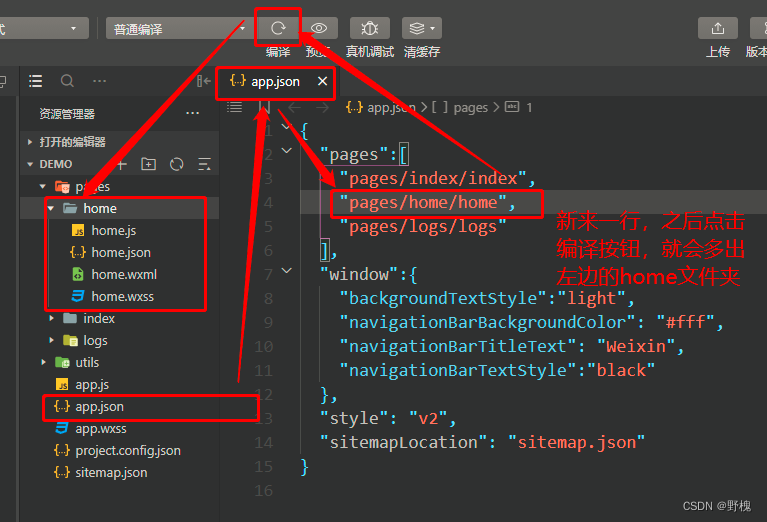

绘制板框

- 手工绘制板框

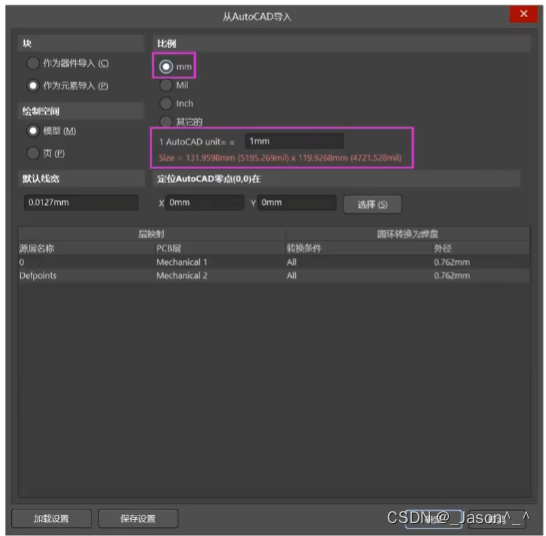

- 导入CAD来定义

注意:单位mm,1:1比例,层设置(或者保持默认)

布局思路流程

按功能模块来分类→准确防止结构器件→理清信号模块分布→理清电源模块分布→放置芯片等大器件→局部模块化布局→整版进行布局优化→布局评审

同时打开原理图和PCB进行布局

模块化区分电路

1.交互选择模式下:利用AD分屏的方式把原理图和PCB同时显示在一个桌面上,方便交互式操作

2.区域内排列器件:在原理图中要选择要区分的电路,切换到PCB中进行区域内排列期间,从而达到把各个电路区分好

Tools → Cross Select Mode (Ctrl + Shift + X) 打开交互选择模式

选中原理图中器件后,进入PCB界面,Tools →Component Placement → Arrange Within Rectangle

快捷键自己设置为Alt + S

器件精准定位

M+S(移动选择),选中要定位的器件,配合器件捕抓功能Shift+E(快捷键)文章来源:https://uudwc.com/A/9gY5

整板大器件位置布局

- 根据已有板框来确定结构件

有一些项目是有专门结构的,这时候我们需要根据 已有的结构来放置结构件 - 自行设计板框及极性定义结构件

没有指定结构的,可以自行按照器件的多少来定义,结构件也可以根据使用方便来自行放置。

模块化布局

模块化能把杂乱无章的元器件快速实现分类,在布局时,多使用模块化,可以提高设计效率。

下面列出一些模块化要注意的事项:

- 按电气性能来分,把模拟部分和数字部分区分

- 发热元件应与温度敏感元件分开放置

- 时钟产生器(如晶振)要尽量靠近用到该时钟的器件;

- 集成电路的电源输入和地之间,要加一个去耦电容

- 布局要求均衡,疏密有序,不能头重脚轻或一头沉

- 以太网口模块要进行隔离处理

- 电源电路要采用“一”字型或“L”型布局方式

整板布局优化

确认最终布局

Class与规则的设置

class创建及作用

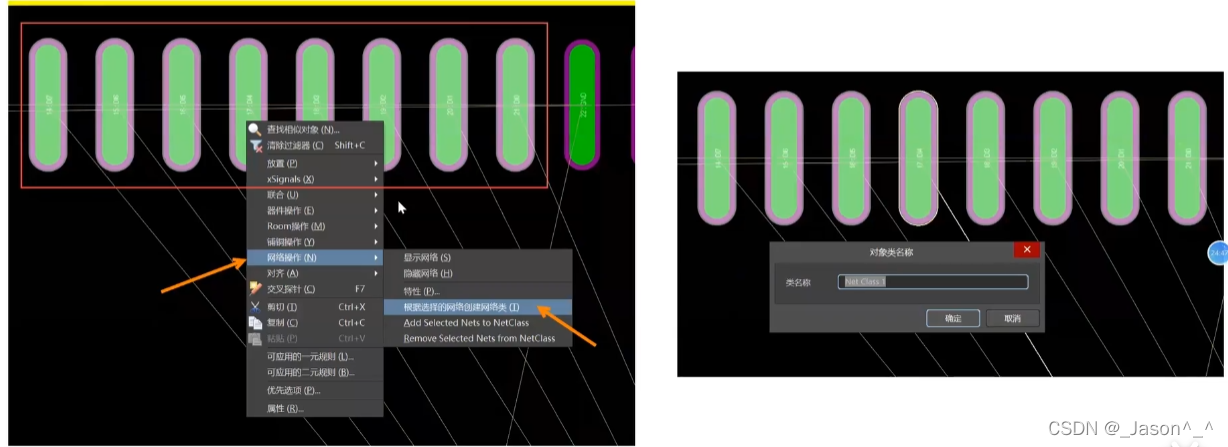

- 常用的创建class的方法

- 选中相应的网络来创建

- 利用设计菜单下面的类来创建

- 选中相应的网络来创建

- 创建class的用途及作用

- 理清不限思路,实现快速布线,提高设计效率

- 统一给相同类型的网路添加颜色

- 统一给相同类型的网路设置规则

- 统一给相同类型的网路交互布线

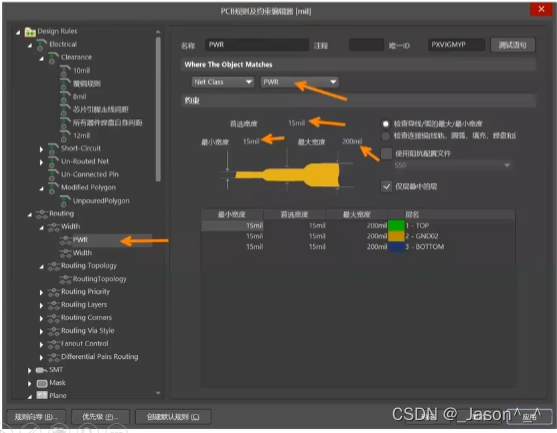

- 创建常用的class的规则

- 电源类的规则

- 高速线类的规则

- 差分类的规则

类的创建与使用

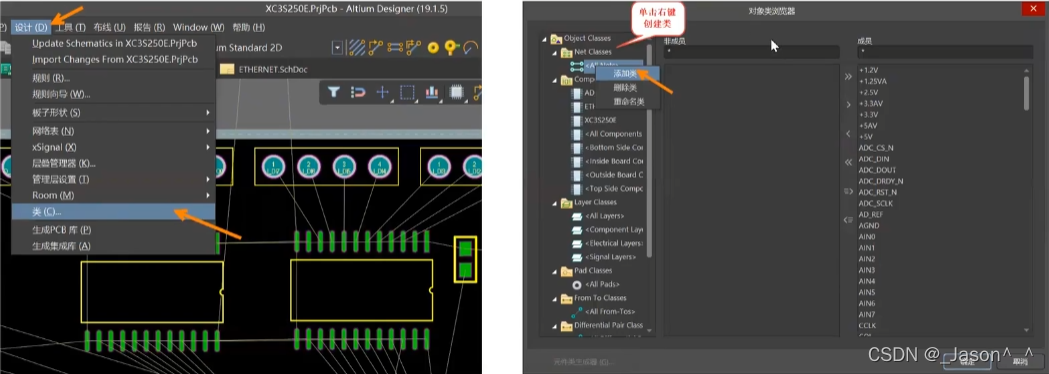

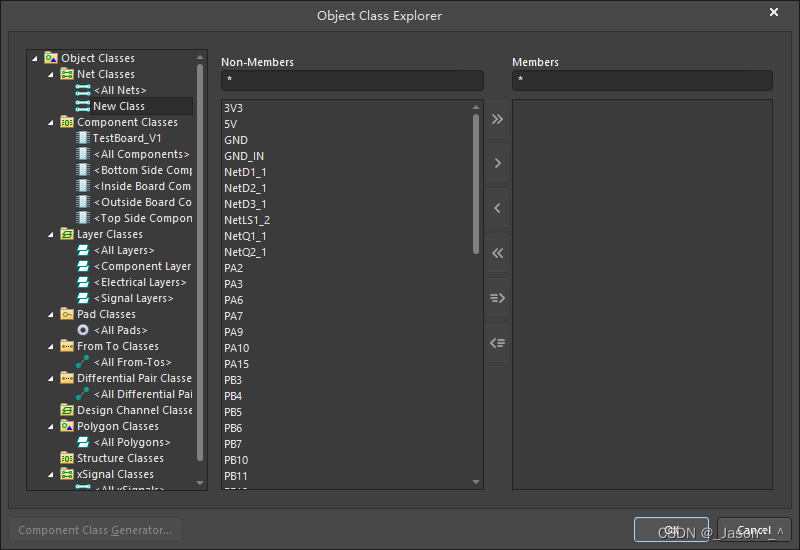

打开“类管理器” Design→Classes Shortcut:DC

重点需要关注的线 需要设置类

- 新建类 NetClasses右键即可新建 还可以删除、重命名

- 双击网络名加入对应的类中也可以点箭头

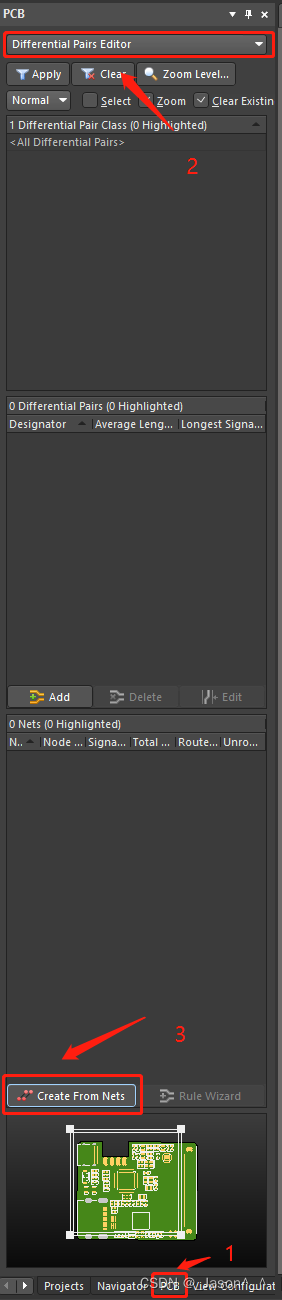

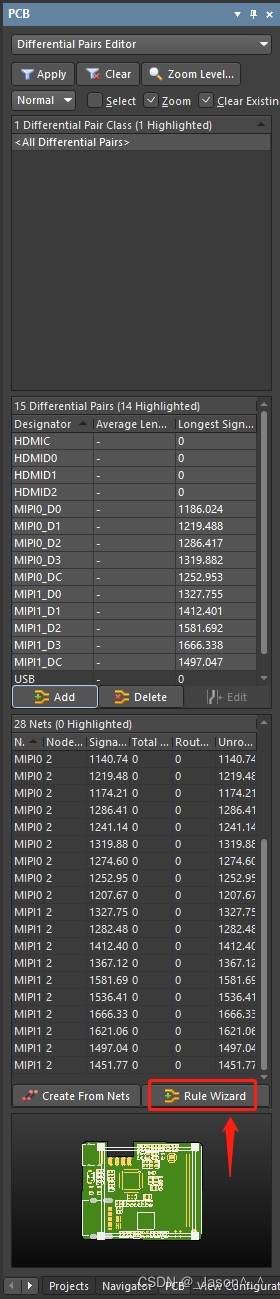

添加差分对

- 打开到PCB界面

- 选择差分对编辑器

- 点击从网络创建

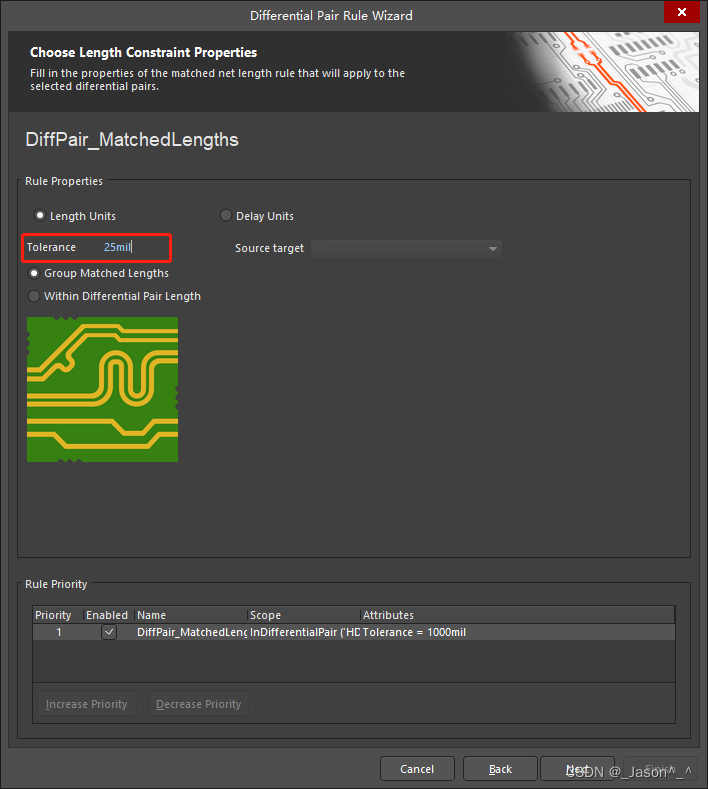

- 添加差分线规则,点击规则向导

- 差分线规则

信号线等长处理

-

对内等长

规则:

-

对间等长

Route→Interactive Diff Pair Length Tuning

走线的时候可以按1234调整

PCB信号线布线

- 从最复杂的地方入手:纵观整板走线的分布,遵守“先大后小,先难后易”的原子来开始布线

- 模块化布线处理:根据每一部分模块的功能来一一进行布线。

- 杂线的处理:整板长线处理完,还有一些闲杂的信号线需要处理,通过这一步我们就能把板子上的所有信号线处理完毕

PCB布线原则

- 布线优先次序

信号线优先:模拟小信号、高速信号、时钟信号和同步信号等关键信号优先布线

密度优先原则:从单板上连接关系最复杂的器件着手布线。从单板上连线最密集的区域开始布线

注意点:

尽量为时钟信号、高频信号、信号提供专门的布线层,并保证最小的回路面积。必要时应采取手工优先布线、屏蔽和加大安全间距等方法。保证信号质量。

电源层和地层之间的EMC环境较差,应避免布置对干扰敏感的信号。

有阻抗要求的网络应尽量按线长线宽要求布线 - 四种具体走线方式

- 时钟的布线:

时钟线是对EMC影响最大的因素之一。在时钟线上应少打过孔,尽量避免和其他信号线并行走线,且应原理一般信号线,避免对信号线的干扰。同时应该避开板上的电源部分,以防止电源和时钟相互干扰。 - 直角走线

直角走线会使传输线的线宽发生变化,造成阻抗的不连续。其实不光是直角走线,钝角,锐角走线都可能会造成阻抗变化的情况。 - 差分走线

抗干扰能力强,能有效抑制EMI,时许定位精确等特征。 - 蛇形线

蛇形线会破坏信号质量,改变传输延时,布线时要尽量避免使用

- 时钟的布线:

PCB布线步骤

- 优先处理小电源网络

- 处理大电源网络

- 电源分割的使用方法

整板走线优化及铺铜处理

- 把不规范的走线进行优化处理

- 把不规则的普通进行优化处理,

- 先铺小铜皮,再铺大铜皮

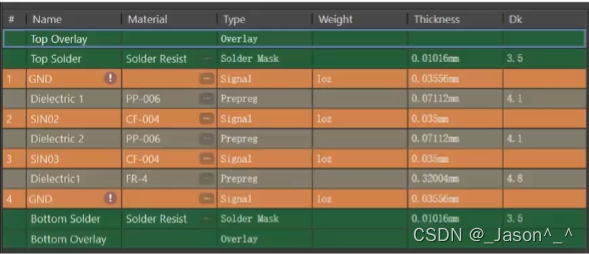

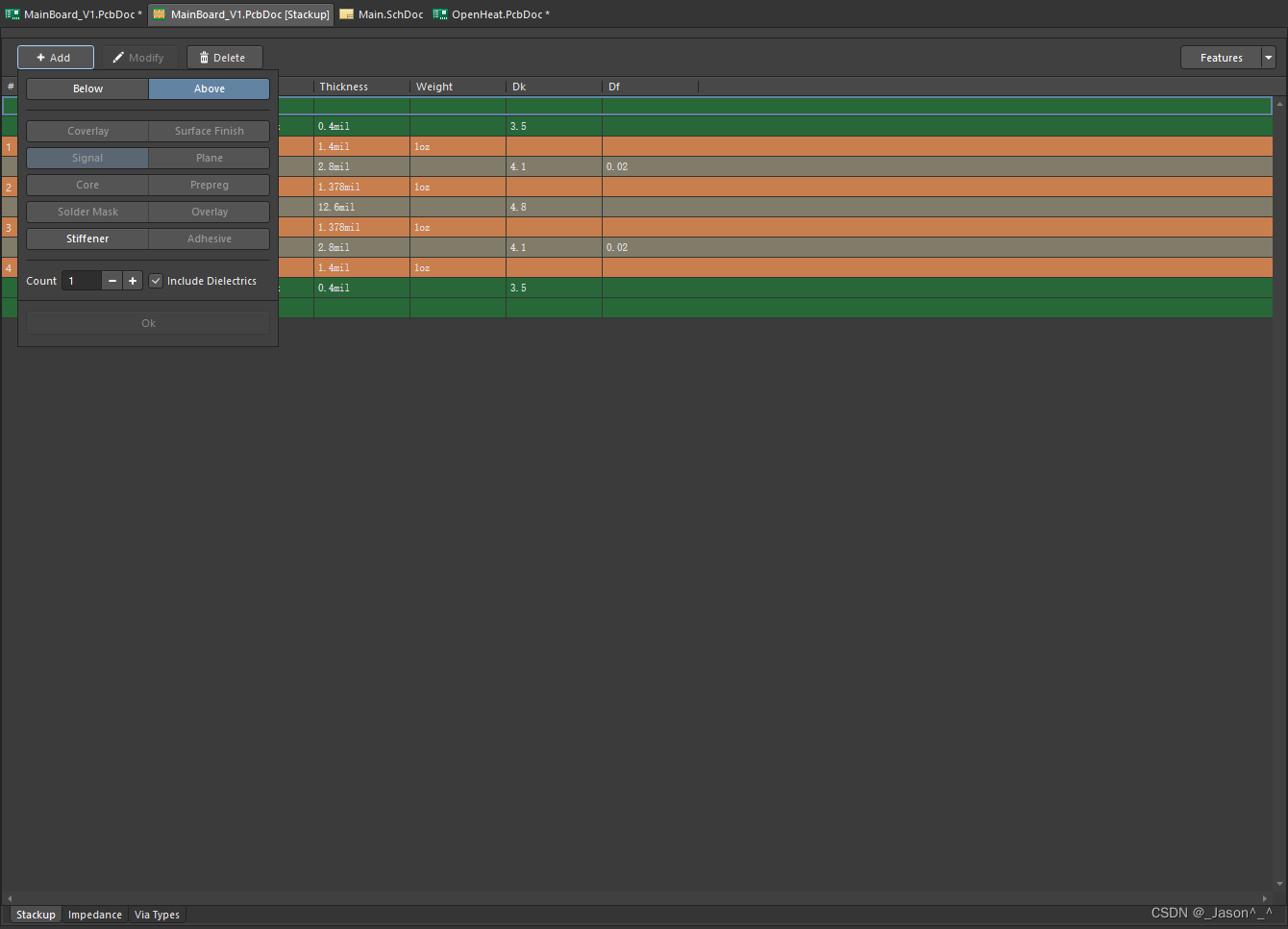

四层叠层设计

电路板的叠层安排是对PCB的整个系统设计的基础。叠层设计如有缺陷,将最终影响到整机的EMC性能。

总的来说叠层设计主要遵从两个规矩:

- 每个走线层都必须有一个邻近的参考层(电源或地层)

- 邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容

1.常规叠层方式

对此种叠层设计,潜在的问题是对于传统的1.6mm(62mil)板厚。层间距将会变得很大,不仅不利于控制阻抗,层间耦合及屏蔽;特别是电源地层之间间距很大,降低了板电容,不利于滤除噪声。

对于第一种方案,通常应用于板上芯片较多的情况。这种方案可得到较好的SI性能,对于EMI性能来说并不是很好,主要通过走线及其他细节来控制。主要注意:底层放在信号最密集的信号的相连层,有利于吸收和抑制辐射;增大板面积,体现20H规则。

2.不常见的叠层方式

对于此种方案,通常应用于板上芯片密度足够低和芯片周围有足够面积(放置所要求的电源覆铜层)的场合。此种方案PCB的外层均为地层,中间两层均为信号/电源层。信号层上的电源用宽线走线,这可使电源电流的路径足控低,且信号微带路径的阻抗也低,也可同故宫外层地屏蔽内层信号辐射。从EMI控制的角度看,这是现有的最佳4层PCB结构。主要注意:中间两层信号、电源混合层的间距要拉开,走线方向垂直,避免出现串扰;适当控制板面积,体现20H规则;如果要控制走线阻抗,上述方案要非常小心的将走线布置在电源和接地铺铜的下面。另外,电源或地层上的铺铜之间应尽可能的互连在一起,以确保DC和低频的连接性。

常见名词解释

正片:所见即所得,在正片层上走线就是将铜覆盖在你走线的地方

负片:若你在负片层走线就相当于在画线的地方把铜去掉了。

添加层

Design→Layer Stack Manager

点击ADD添加层,选择上方/下方添加

选择添加类型,signal正片层,plane负片层

设计原则列举(self)

对于自己画板子最好每次遵守相同的原则可以有利于养成习惯。

每个人可以有不同的习惯,我会在下面列举一些我自己的习惯。

原理图原则

- 器件的comment:标出该器件的具体参数,并且显示。例如容值、阻值、耐压、功率……

- 器件的description:标出元件的具体种类。比如这个元件是一个电阻,在description中就标注是贴片电阻or直插电阻or……

- 标注单位时同一类型统一标注。

PCB原则

问题及解决方案

Q1 AD原理自动编号

Tools -> Annotation ->Annotate Schematics

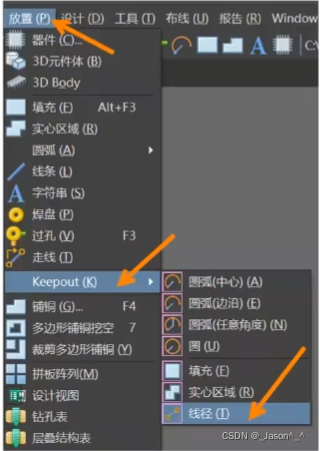

Q2 确定板子大小

选keepout线->按Tab->Design->Board Shape->Define Board Shape From selected objects

Q3 报错

Silk To Silk Clearance Constraint Violation

丝印对丝印间隙约束违反

其实这些错误都是丝印层和丝印层或者是丝印层和阻焊层之间间距大小引起的问题,这是封装引起的问题,一般情况下问题不大,可以忽略,如果想去掉这个错误的话要么改封装,要么改规则设置

Silk To Solder Mask Clearance Constraint Violation

改Rules

在【设计规则检查】中取消这个规则的检查

Q4 导出器件清单

打开PCB工程→打开PCB文件→点击Reports选项卡→点击Bill of Materials→选择显示属性、排序、到处文件格式→导出

Q5 多个原理图多个PCB,如何对应导入?

- 在原理图编辑界面执行菜单栏中“工程”→“显示差异”,弹出“选择比较文档”对话框

- 在“选择比较文档”对话框中,勾选左下角“高级模式”复选框,对话框将显示称两个专栏

- 选择需要比较的文档,左侧选择SCH,右侧选择对应PCB文件,点击确定按钮

- 弹出Differences between Schematic Document […] and PCB Document […]

- 单击鼠标右键,执行Update All in>>PCB Document[…]

- 在执行完步骤5之后,单击左下角“创建工程变更列表”,这时弹出“工程变更命令”对话框,之后的操作跟菜单栏中Design→Update PCB Document xxx.PcbDoc命令的操作方法一样

Q6 如何设置原点

Edit→Origin→Set

Q7 AD的3D视图操作

在3D视图下旋转PCB板 shift+鼠标右键

Q8 设置tool bar

在bar区域,右键选择customize→toolbar选择需要工具栏

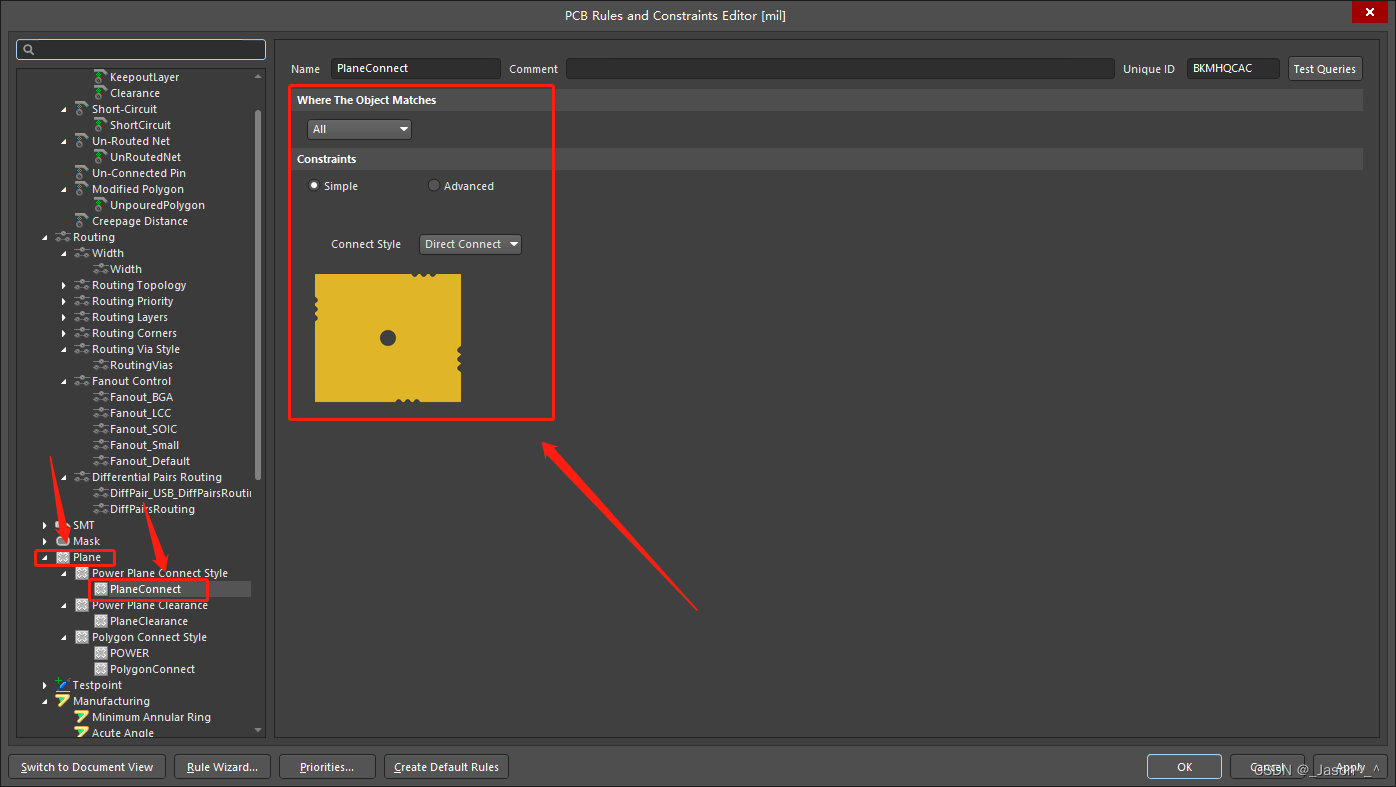

Q9 焊盘连接选择

通孔、散热量大的元器件使用十字连接,如果觉得十字连接连接线太短可以更改。而如果不需要考虑散热的一般可以采用直接连接

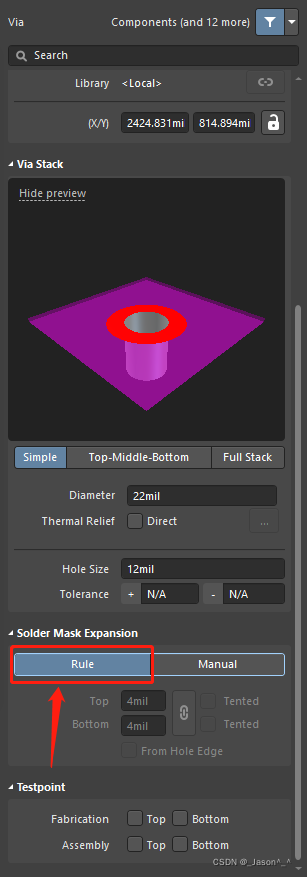

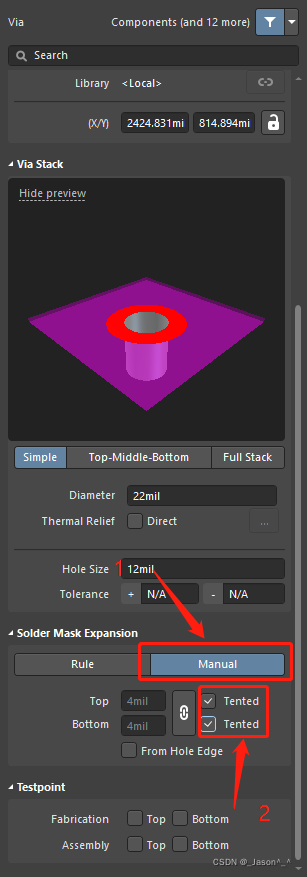

Q10 过孔盖油和过孔开窗

过孔开窗

过孔盖油

总的来说,勾选是盖油

不勾是开窗

若勾选了之后,再点Rule,之后的过孔默认为Manual更改之后的过孔模式

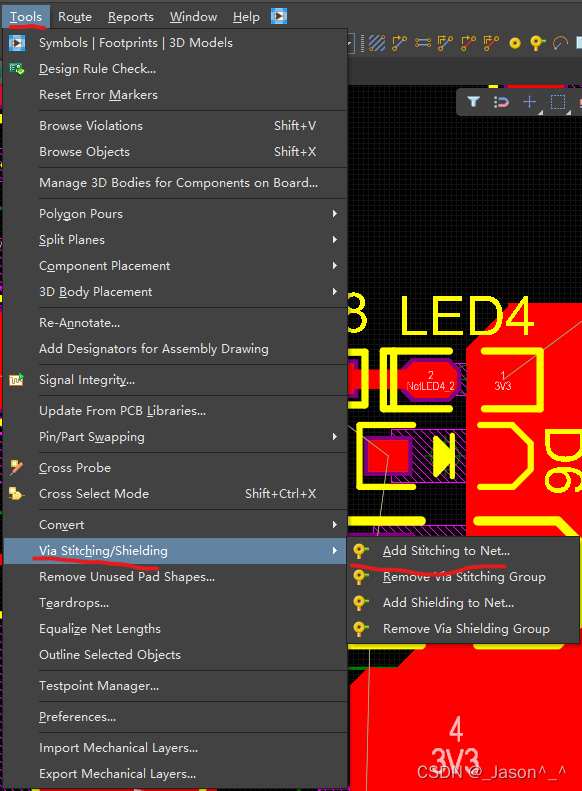

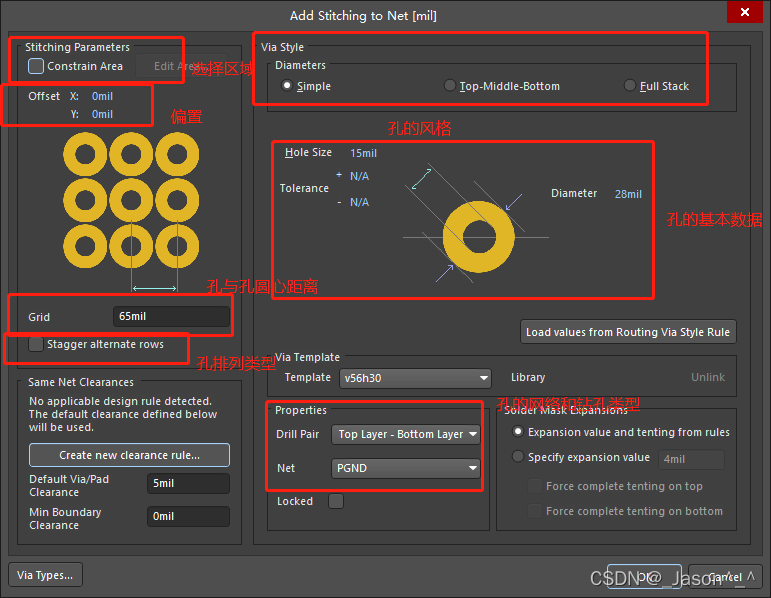

Q11 批量添加缝合孔

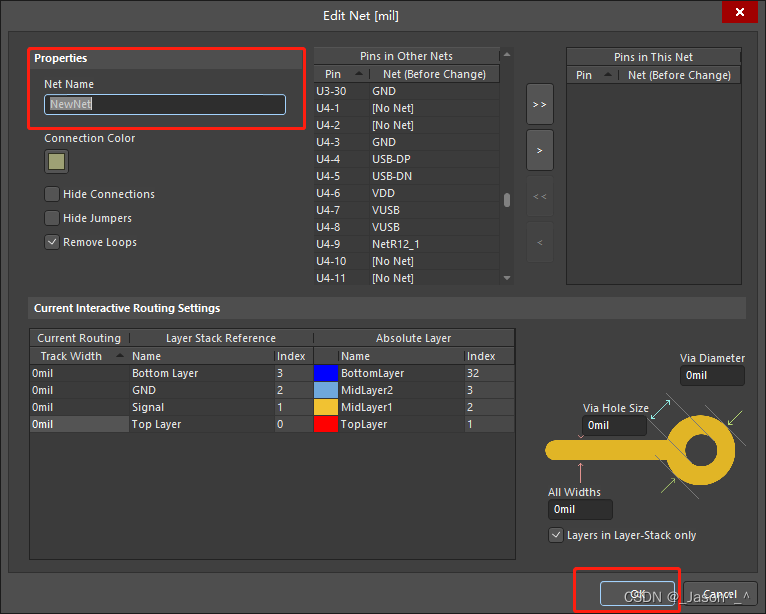

Q12 PCB中想要单独添加一个原理图中没有的网络

输入网络名,点击ok就可以了

Q13 如何隐藏飞线

按快捷键"N",Hide Connections

Q14 快捷键N失效了怎么办

查找AD手册发现

检查ToolBar

在File的那一行空白处右键,Customized,Toolbars,勾选上Popups

Q15 负片层过孔铺铜连接形式修改

常用组合

线宽:

信号线:6mil

电源线:输入电源=一般铺铜;

过孔:holesize=10mil , diameter=18mil

嘉立创规则

| 项目 | 加工能力 | 工艺详解 |

|---|---|---|

| 钻孔孔径( 机械钻) | 0.2~6.3mm | 最小孔径0.2mm,最大孔径6.3mm,如果大于6.3mm工厂要另行处理。机械钻头规格为0.05mm为一阶,如0.2,0.3mm |

| 线宽 | 3.5mil | 多层板3.5mil 单双面板5 mil (1OZ完成铜厚),2OZ完成铜厚最小线宽线隙8mil |

| 线隙 | 3.5mil | 多层板3.5mil 单双面板5 mil (1OZ完成铜厚),2OZ完成铜厚最小线宽线隙8mil |

| 最小过孔内径 及外径 | 内径(hole)最小0.2mm,外径(diameter)最小0.4mm | 多层板最小内径0.2mm,最小外径为0.4mm,双面板最小内径0.3mm,最小外径0.5mm |

| 焊盘边缘到线距离 | 5mil | 参数为极限值,尽量大于此参数 |

| 最小字符宽 | 线宽6mil 字符高40mil | 参数为极限值,尽量大于此参数 |

| 单片出货:走线和焊盘距板边距离 | ≥0.3mm | 否则可能涉及到板内的线路及焊盘 |

| 拼版V割出货: 走线和焊盘距板边距离 | ≥0.4mm | 否则可能涉及到板内的线路及焊盘,如右图,如果是拼版,则线离边必须要有0.4mm间距,否则v割会伤到线路。如果是单片出货,则需要≥0.2mm的间距。 |

| 最小工艺边 | 3mm | |

| 拼板:无间隙拼板 | 0mm间隙拼板 | 板子与板子的间隙为0mm。 |

| 拼板:有间隙拼板 | 1.6mm间隙拼板 | 有间隙拼版的间隙不要小于2.0mm,否则锣边时比较困难。 |

| 半孔工艺最小孔径 | 0.6mm | 半孔工艺是一种特殊工艺,最小孔径不得小于0.6mm。小于0.6MM做不出半孔的效果 |

| 阻焊层开窗 | 0.05mm | 绿油桥小于3mil不保留,绿油桥大于3mil保留,不以阻焊桥为检验出货标准,因阻焊桥不影响到性能,不接受阻焊桥客诉!阻焊桥能力:绿油桥最小3mil,其它杂色油墨最小4mil |

快捷方式汇总

原理图

Shift+E

画线时使用此快捷键可实现捕捉功能

Alt+左键

高亮相同网络

删除器件或线

E+D

PCB

Ctrl+左键

高亮相同网络

Ctrl+左键

高亮相同网络

Shift+C

清除Filter

D+S+D

快速定义板子大小

S+L

线选

排列器件

按“A”,然后选择想要的想要的排列顺序。

器件精准定位

M+S(移动选择),选中要定位的器件,配合器件捕抓功能Shift+E(快捷键)

显示某一特殊的层

Shift+S文章来源地址https://uudwc.com/A/9gY5