最近在做一个项目,需要使用到高精度的ADC采集,由于项目对采集速率并没有太高的要求,所以就将成本尽可能地花在采样精度上,最后选择了TI的ADS1256这款比较热门的24位高精度AD芯片,调完后来写篇文章记录一下。

手册分析

老规矩,在介绍如何用FPGA控制其进行AD转换之前先来聊聊它的数据手册。

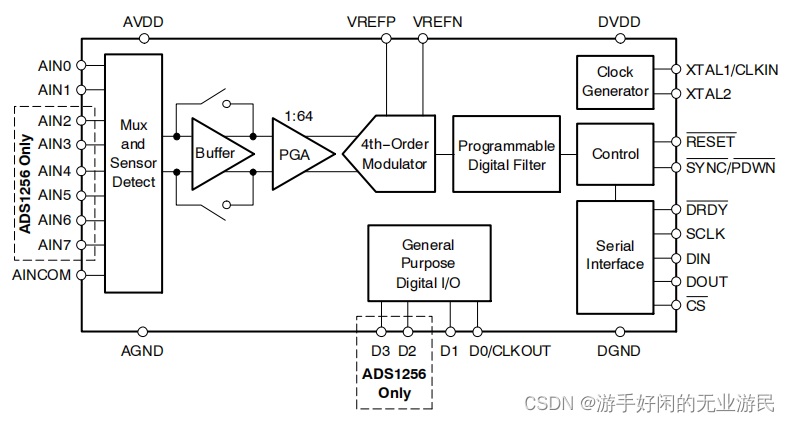

(1) 框图以及引脚介绍

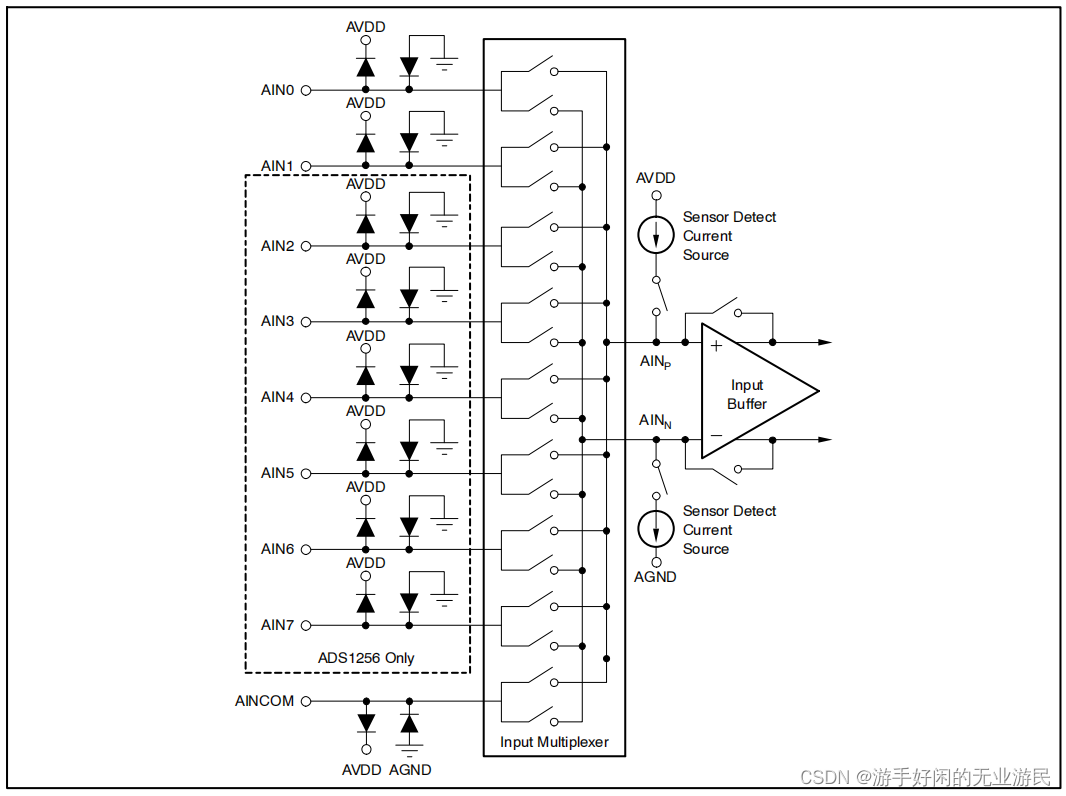

如上所示为ADS1256的整体框图,从左到右为整片的测量顺序,模拟输入经过选择器后到Buffer,然后是PGA,再是模数转换单元,最后是通信和时钟接口,一目了然,下面介绍一下该芯片的引脚。

(左图为ADS1255,使用方式和ADS1256一摸一样,只是片内资源少了许多,改一下寄存器配置即可,如若不需要太多的测量通道的话可以使用,节省成本。)

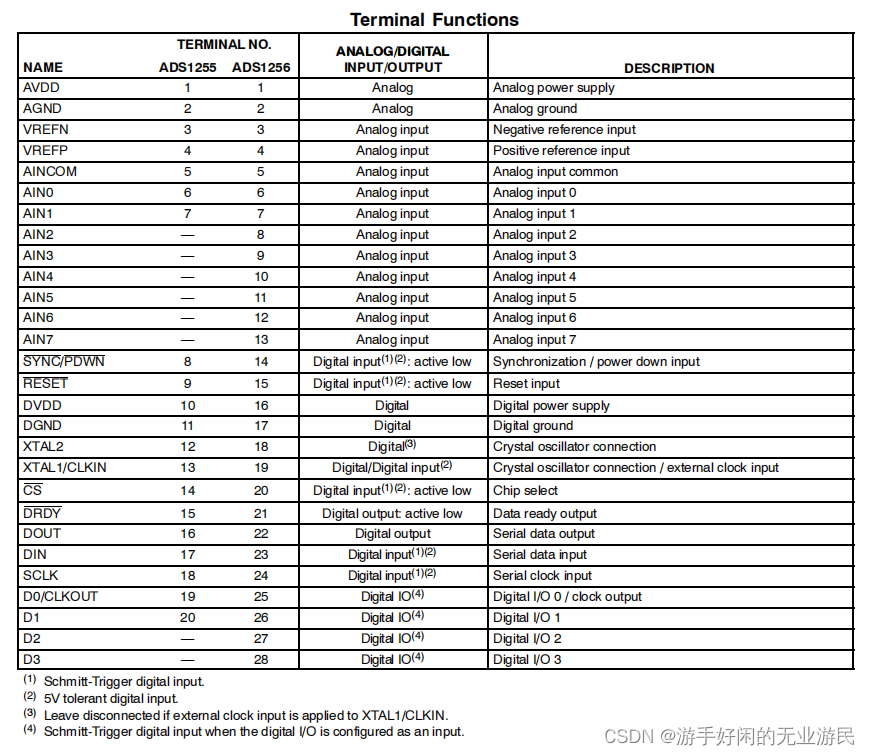

对于上述的引脚说明:

- 电源部分不再多说,区分好数字地和模拟地即可。再是参考电压的选择,本人选择的是VrefP接2.5V,N端接模拟地,即设置参考电压为2.5V。

- 随后是9个模拟输入口,一般来说AINCOM端口直接接到AGND上去,作为单端输入使用的N端口(这个后面细说)。其他模拟输入口则悬空处理,等待模拟量输入。

- 然后介绍SYNC/PDWN引脚,该引脚用来同步,从本文将要介绍的测量方式来说,当我们开始测量的时候选择拉低这个引脚一段时间进行同步(具体多久手册上有说明,实际上是一个很宽的范围),当同步结束后即可读取测量的数据,同步的方式也可以通过SPI发送指令开始同步,这样第一节省资源,第二简单方便,所以本设计不采用引脚同步,将其接到高电平,选择指令同步方式。

- DRDY接口,一个很重要的接口,ADS1256内部转换有相当多的时序,如果靠用户一一去计数进行操作会相当麻烦,而且无法保证数据准确,DRDY接口表示当前数据可读,也就是说每当我们进行测量操作后,只有当DRDY引脚拉低后才能进行数据读取,此外,当我们对芯片进行复位、初始化后也需要等待DRDY引脚拉低,表明复位或者初始化完成,之后才能进一步通信,进行测量。

- 最后就是四个SPI接口了,相信大家都很熟悉,MISO即DOUT,ADS1256传数据给FPGA的端口;MOSI即DIN,FPGA传数据给ADS1256的端口,CS选通,SCK时钟信号。

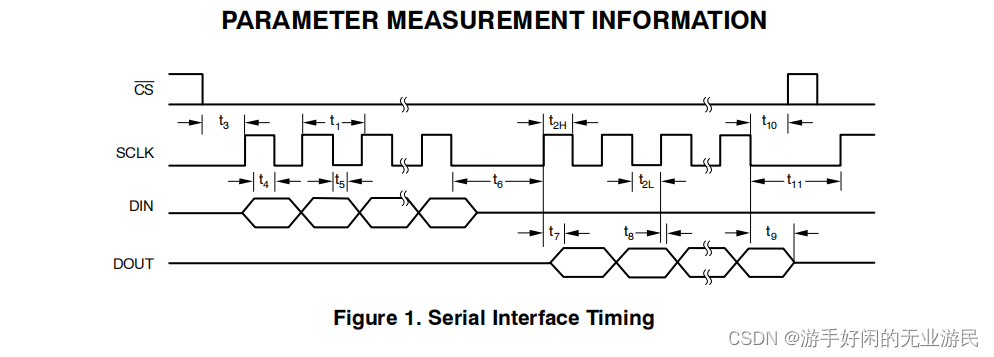

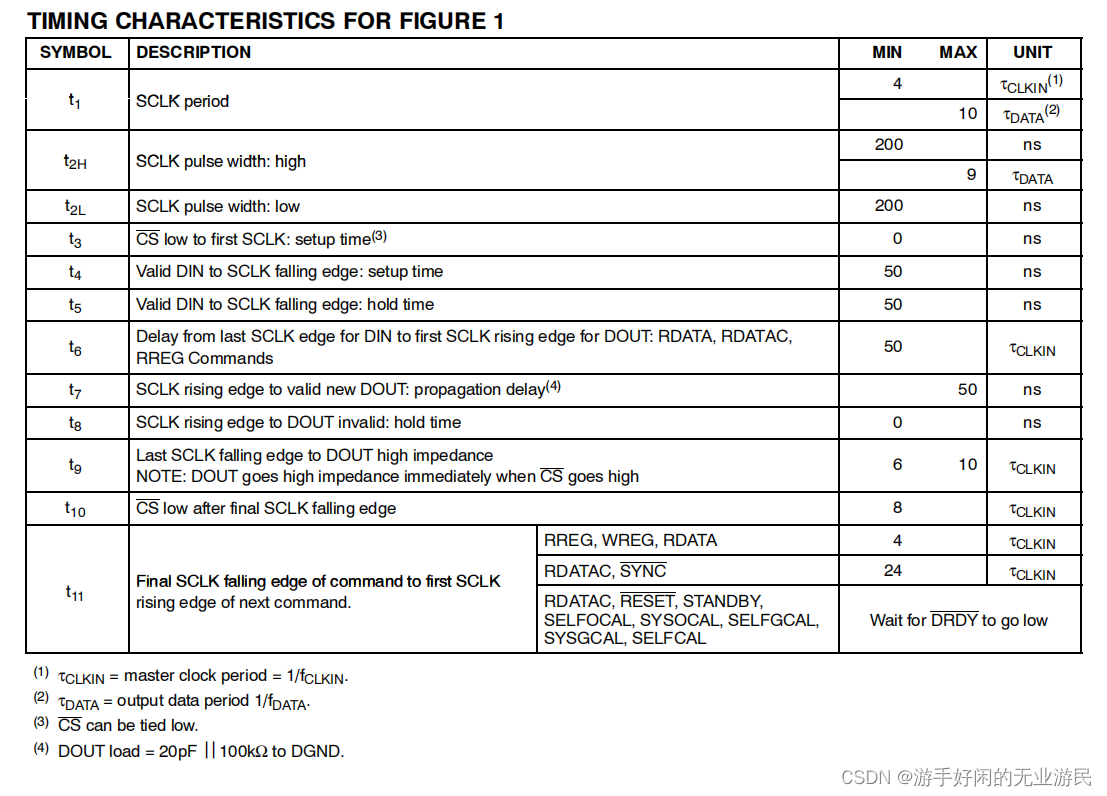

(2) 通信时序

ADS1256的SPI通信和大多数的SPI芯片一样,CS选中之后即可开始通信,下降沿的时候发送和接收数据(所以对于FPGA而言,下降沿的时候把数据读进,但是在发送数据的时候上升沿将数据准备好,那么下降沿的时候发送出去即可,这个应该好理解)需要注意的是通信的时序,这边挑几个重要的进行讲解:

- 首先就是t1,SCK的周期,从上图中我们可以看出SCK时钟周期既有上限也有下限,所以需要挑一个合适的中间值。由上可见,tCLKIN为输入时钟源的周期,时钟源为一个7.68MHz的石英晶振,所以一个周期大约为0.13us,tDATA表示设定的采样速率,预计的采样速率为1000Hz,所以采样周期为1ms,这样一来我们所设置的SCK周期只需要在4 × 0.13 = 0.52us到10 × 1ms = 10ms之间即可。我们选择10us的SCK周期,即5us高电平,5us低电平即可。

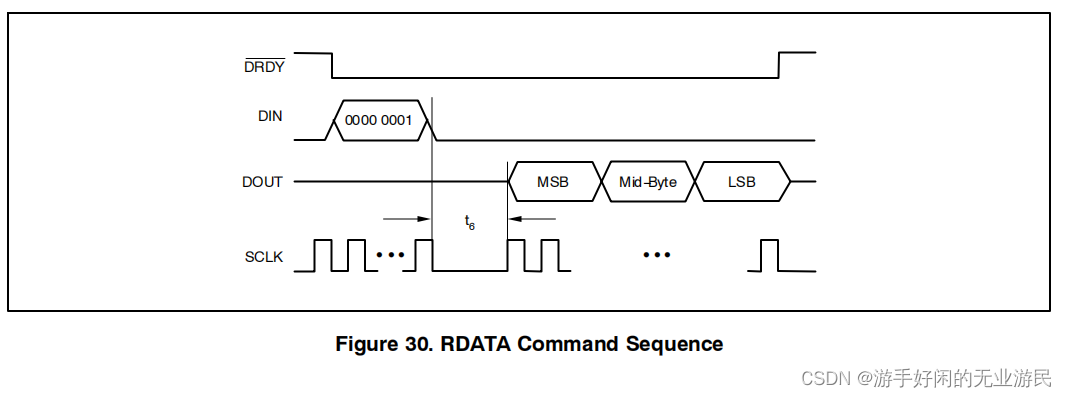

- 第二讲一下t6,它表示你给如一个读操作的指令,到数据输出的一个间隔,可以理解为读指令和数据输出的一个等待间隔,最小为50 × 0.13 = 6.5us,所以这里我们设定为20us。

- 第三讲一下t3和t10,表示CS变化到SCK变化的时间间隔,这里我们也设置为5us。

- 第四,相当重要的一个时间段,t11,表示当前指令结束到下一个指令开始的时间间隔。从上图中我们看出不同的指令所需要的时间周期也不同。我们在实操的过程中必须严格按照手册中所述的时间间隔进行操作,否则大概率是得不到正确结果的(血的教训,本人调了好久这块芯片,一开始由于度手册不仔细数据一直出错,后来还是得认认真真细读手册,最后才出结果)。

- 最后提醒一下,上表中没有提到两个CS周期之间CS需要拉高的时间间隔,但是我们在操作的过程中最好留一下,所以我在每一个指令输出的过程中都给了CS一个5us的拉高时间,之后才拉低进入通信,这个在后面看我代码的时候注意一下即可。

好了,讲了这么多,大家一定也发现了,上面介绍的5us也好,20us也罢,都是5us的倍数,所以我们只需要在程序中定义一个5us的计数器,再对结果进行计数即可得到对应的延时时间。

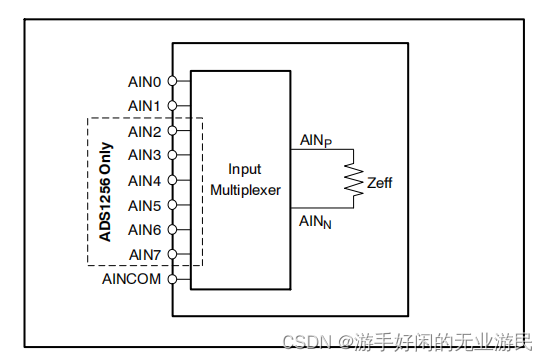

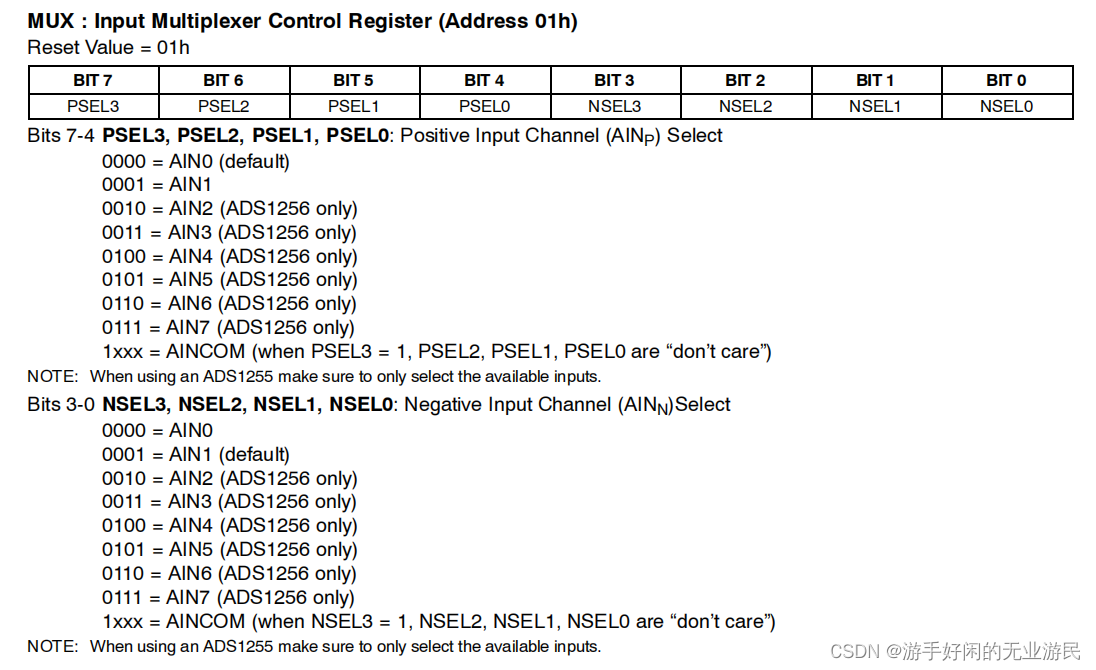

(3) 通道选择

由上图可见我们可以选择任意两个通道作为P、N段的输入,实际上ADS1256在工作的时候就是测量的AINP-AINN的电压,如果你的硬件条件只需要单端测量,后面对于寄存器的配置时将N段配置为AINCOM(接地)即可。

(4)其他特殊功能

ADS1256的功能相当强大,如果从头到尾全部讲完第一篇幅太长不合适,第二大部分都用不到浪费大家时间,所以一下只列出重要的几个讲解。

- 开启Buffer,ADS1256可以配置为高输入阻抗的状态,通过开启Buffer将会呈现出一个约80M的输入阻抗,但同样是有代价的,开启后所能测量的电压范围将会变小,具体测量上限约为AVDD-2.0V。本次设计中未开启。

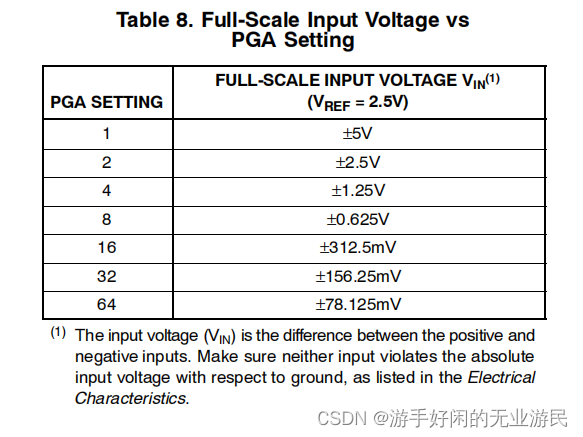

- PGA设置,即内部增益放大器。如若你所测量的信号幅值很小,可以开启PGA对你所测的电压进行放大,当然,放大后的电压不可超过上限 2 × Vref,放大倍数可控。

好啦,就讲这么多,如果你需要更多的功能实现,详情可以阅读手册,或者评论区和我交流。下面介绍本文的重头戏,测量时序。

(3)测量时序

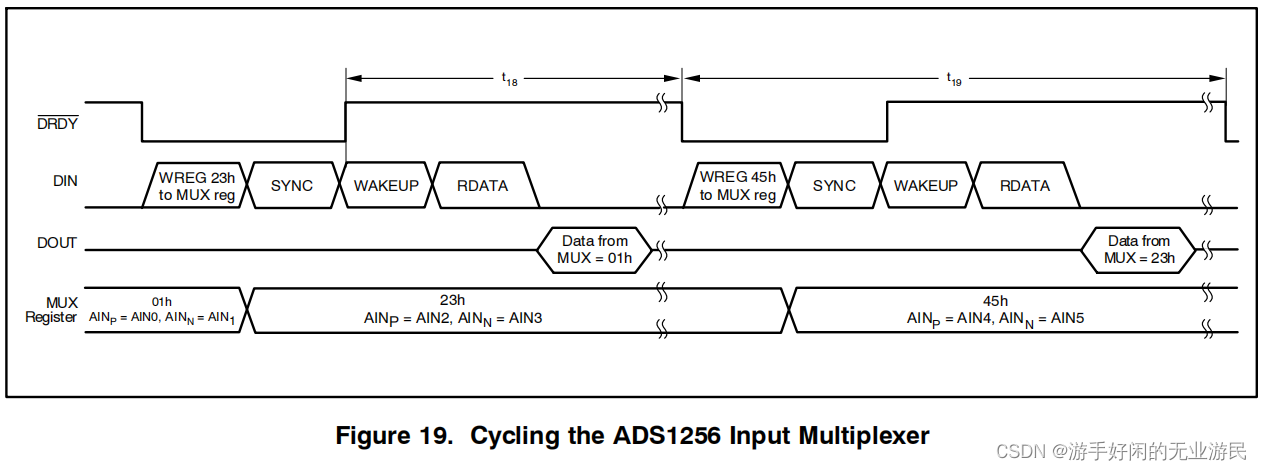

首先在介绍时序之前我想先来说一下ADS1256的测量模式,根据手册上说,总共有四种测量模式,而本次设计则选用最常用的一种测量方式“Using the Input Multiplexer”来进行AD转换。测量时序如下所示:

由上图可见当DRDY拉低表示数据可读之后,主控向其连续发送四个指令后即可读出数据,很简单的操作流程,但是大家需要注意的是每一个指令都有属于自己的周期,指令和指令之间不是连续发送的,每当一个指令周期结束后,需要拉高CS结束一个指令周期,然后再拉低开启下一个指令周期,本设计中我给的每一个CS高电平间隔为5us,以保证满足上述t11的要求。此外,当最后一个RDATA指令发出后,到数据读出还有一个时间间隔t6,这也是我们所需要考虑的,本设计中给定为20us。

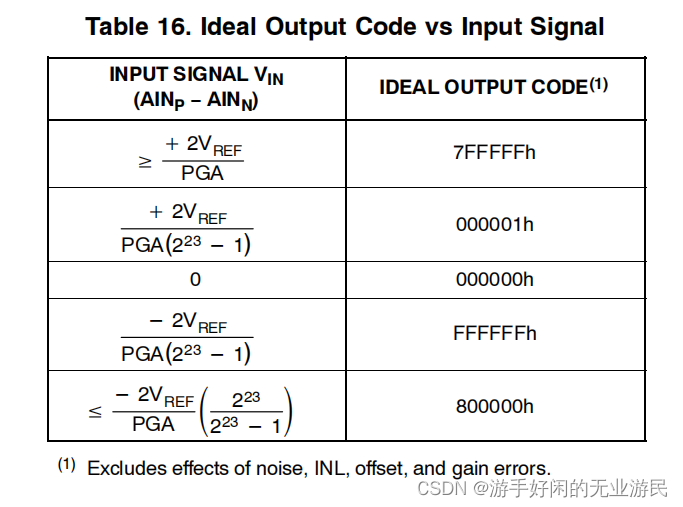

(4)数据格式

上图给出了对应电压的数据格式,当你的输入超过上限呈现为7FFFFFh,0V呈现为000000h,负的电压一样,不过采取补码的方式存储。

(5)校准

每一次测量之前都建议大家对ADS1256进行校准,本设计在上电后进行一次复位,一次初始化,一次校准,之后开始一直测量。而复位后、初始化后、校准后都需要等待DRDY信号拉低表示完毕,测量也是等待DRDY拉低表明数据可读。

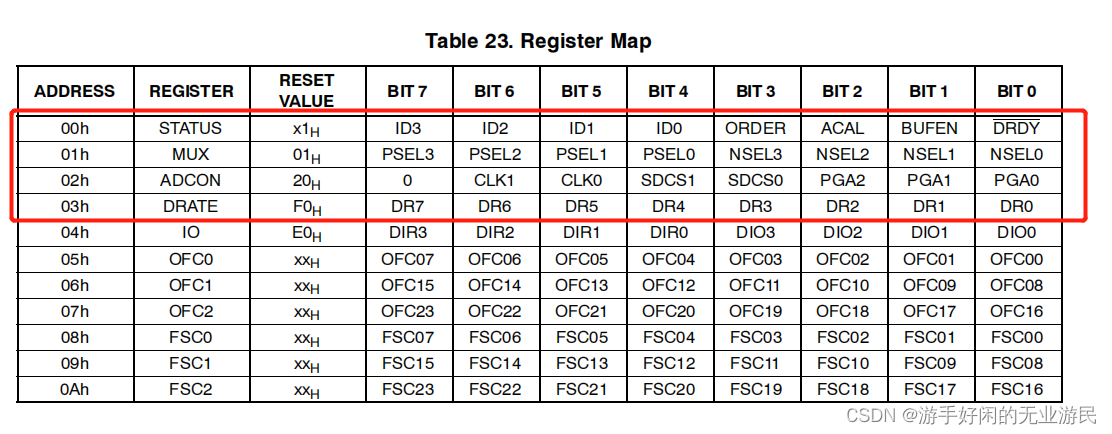

(6)寄存器介绍

寄存器只需要掌握前面四个即可,IO寄存器控制D0-D3端口,没用到,后两个存储对应的滤波分频数,可以尝试的去读一下,更多功能本人也没深究过。

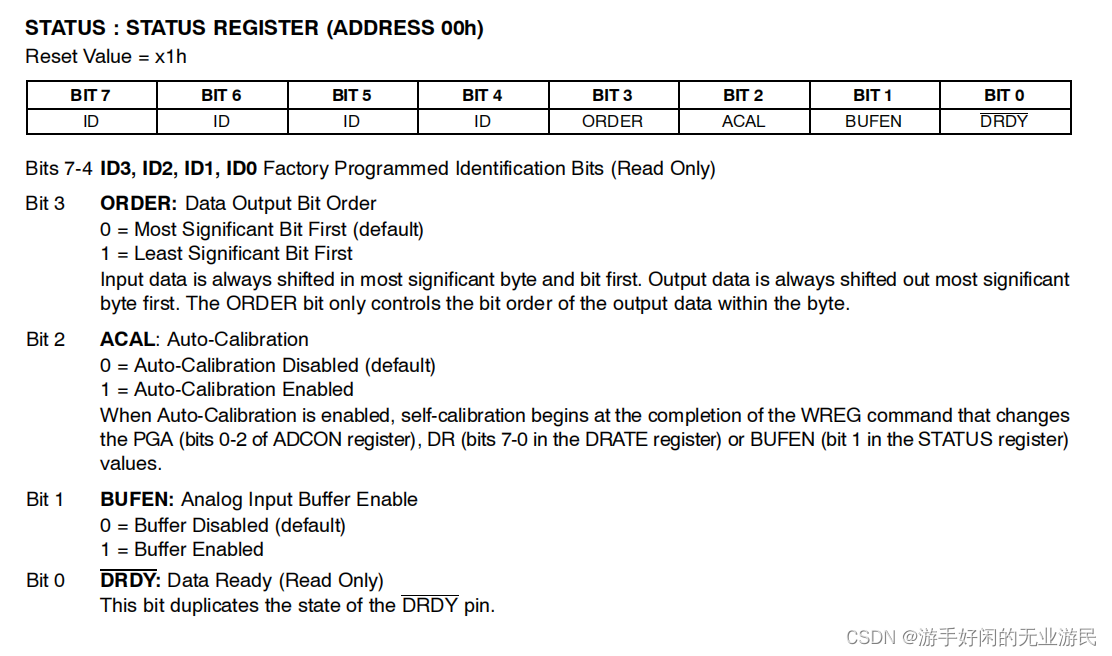

- STATUS寄存器

高四位固定,第四位设置数据为MSB还是LSB,上电后默认为MSB这个我们不需要去更改;ACAL表示是否开启子校准,开启后每次更改PGA倍数、采样率和BUFFER是否开启后都会进行一次自动校准;BUFEN选择是否开启Buffer,DRDY只读,状态和DRDY引脚一致。 - MUX寄存器

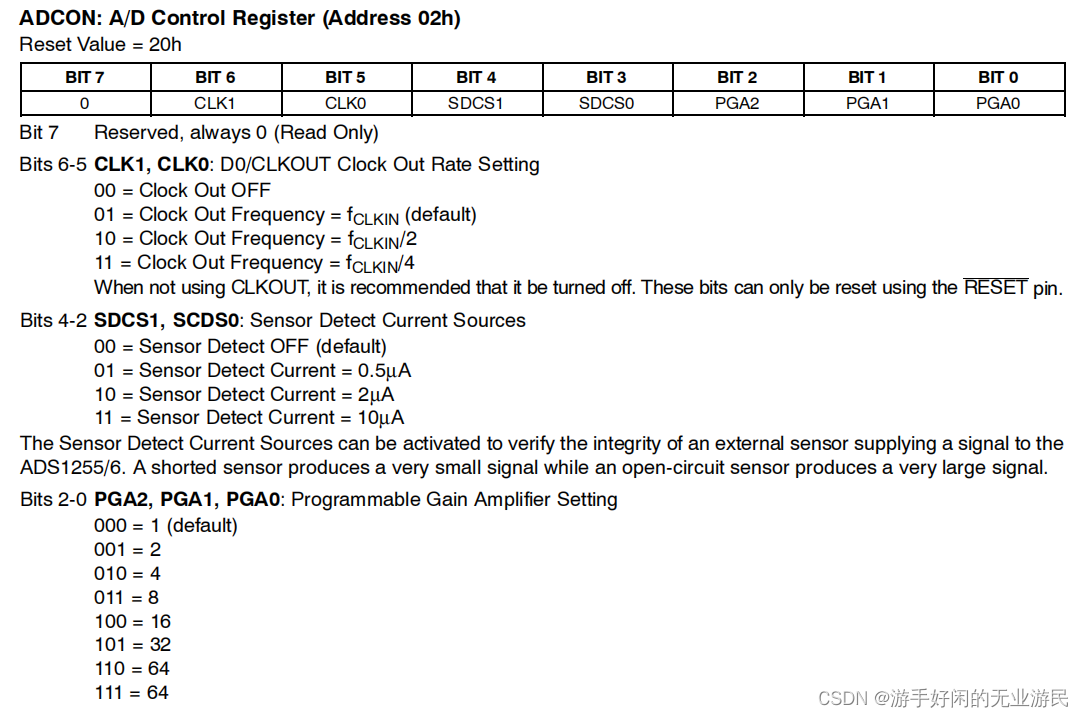

高四位控制AINP的端口,低四位控制AINN的端口输入,最终测的电压就是AINP-AINN。 - AD CON寄存器

低三位表示控制的PGA倍数(放大倍数),第七位只读,剩下四位控制时钟输出以及电流检测,我们没用到,保持默认即可。 - DRATE寄存器

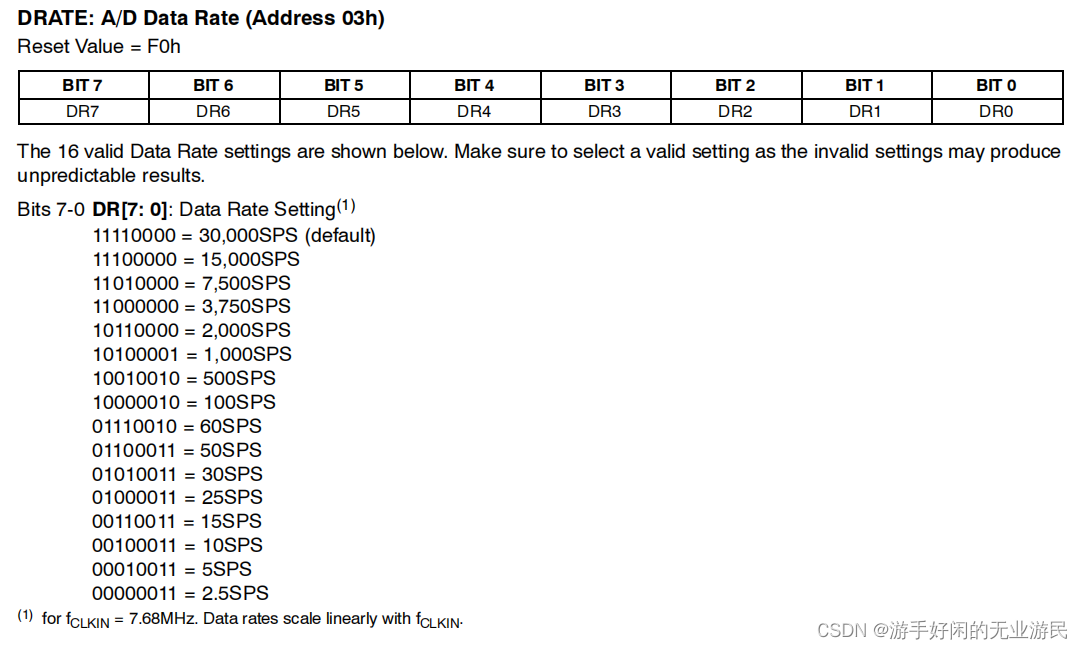

采样速率设定,这个不用多介绍,本设计设置为10100001,每秒1000次。(可见该芯片最高也只能到30k)

(7) 指令表

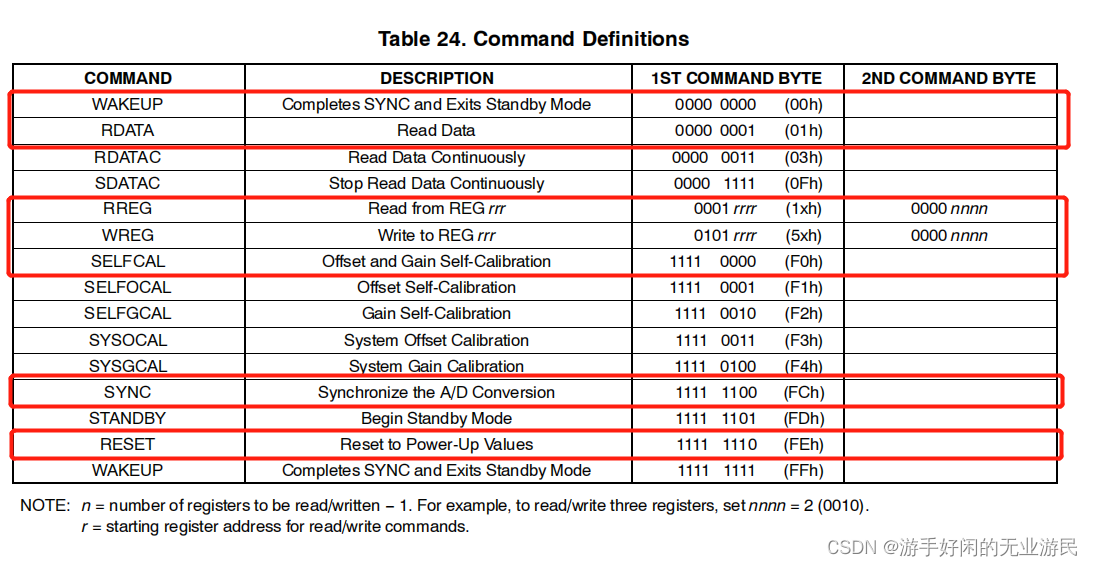

同样的我们也只需要使用到上述指令(SELFCAL别看错了,不是SYSGAL指令)。下面来一一介绍文章来源:https://uudwc.com/A/AAar

- RDATA: Read Data

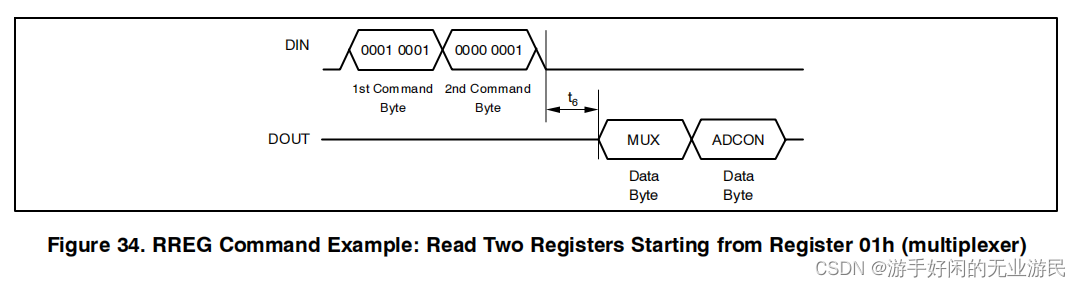

读指令的操作很简单,注意指令下达完毕后等待t6的时间间隔即可。MSB在前。 - RREG: Read from Registers

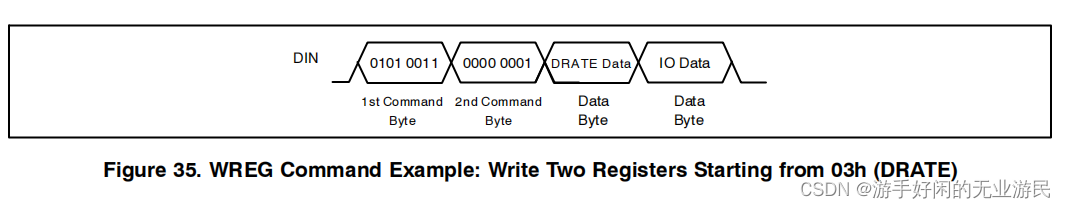

读寄存器指令分为两个字节,第一个字节高四位表示指令,第四位表示读的地址,第二个字节表示从该地址开始读几个寄存器的数据的个数 -1 (eg:只读一个,那么这个值就设置为0x00即可),地址自动递增。 - WREG: Write to Register

写寄存器和读寄存器一样,也是两个字节,操作方式一摸一样,第一个字节指令加地址,第二个字节为长度-1,地址递增。 - SELFCAL: Self Offset and Gain Calibration

这个指令用来进行校准。 - SYNC: Synchronize the A/D Conversion + WAKEUP: Complete Synchronization or Exit Standby Mode

这两个指令要一起用(当然是在不同的指令周期),SYNC之后下一个指令周期要跟一个WAKEUP指令,用来进行同步操作。 - RESET

这个指令我没用到,因为本设计直接采用RESET引脚来复位,圈出来只是告诉大家有时用到复位的操作,以及注意一下复位的时长为5us。

结语

这篇文章已经讲了很多了,再多就不礼貌了。代码工程老规矩放到第二篇来讲。希望大家能够熟读手册后再来进行代码编写,否则有可能会变得不幸。。。文章来源地址https://uudwc.com/A/AAar