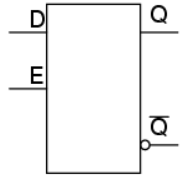

1、锁存器

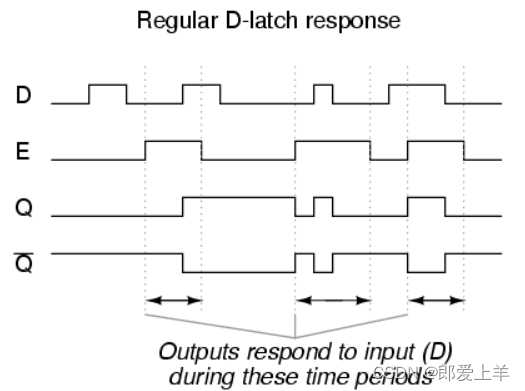

锁存器对脉冲的电平敏感,也就是电平触发,在有效的电平下,锁存器处于使能状态,输出随着输入发生变化,此时它不锁存信号,就像一个缓冲器一样;在锁存器没有使能时,则数据被锁住,输入信号不起作用,此时输出一直为锁存的状态信息(锁存最后一拍数据)。我们常见的锁存器有SR锁存器、D锁存器、JK锁存器等

1.1、锁存器工作原理

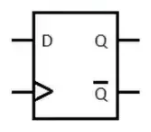

其中D为输入信号,当E为高时,输出Q即为输入的D;当E为低时,Q保持E为高时的最后一次状态,也就是锁存过程。

1.2、锁存器优缺点

优点:面积小。锁存器比FF快,所以用在地址锁存是很合适的,不过一定要保证所有的latch输入源的质量(锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。asic中latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多)。

缺点:

a、容易产生毛刺

b、资源浪费:在Xilinx的FPGA中,6 系列之前的器件中都有Latch;6系列和7系列的FPGA中,一个Slice中有50%的storage element可以被配置为Latch或者Flip-Flop,另外一半只能被配置为Flip-Flop。比如7系列FPGA中,一个Slice中有8个Flip-Flop,如果被配置成了Latch,该Slice的另外4个Flip-Flop就不能用了。

c、时序分析较困难:由于锁存器当通常不包含时钟,造成静态时序的分析困难。

2、D触发器

触发器(Flip-Flop,简写为 FF),也叫双稳态门,又称双稳态触发器。对边沿敏感,也就是边沿触发。

2.1、锁存器工作原理

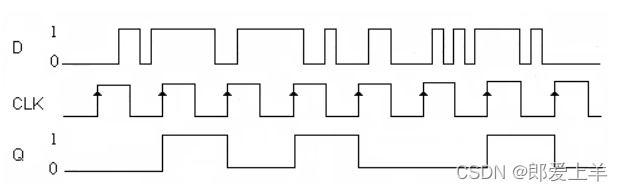

触发器只在时钟边沿时起作用,所以哪怕输入的信号中有毛刺,输出还是比较干净的。FPGA当中使用最多就是触发器。

3、寄存器

用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果,它被广泛的用于各类数字系统和计算机中。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。工程中的寄存器一般按计算机中字节的位数设计,所以一般有8位寄存器、16位寄存器等。

4、RTL代码产生锁存器

时序逻辑不会出现锁存器,组合逻辑在特定情况下会综合出锁存器或者说边沿沿敏感的语句只会综合出触发器,电平敏感的语句在覆盖不全时会出现锁存器(典型的if…else…或case…default…语句不完整,也就是出现了信号保持)。

1)

always @(*)begin

if(d)

a = b;

end

2)

always @()begin

if(d)

a = b;

else

a = a;

end

3)

always @ (b or d)

case(d)

2’b00: a=b>>1;

2’b11: c=b>>1;

default:begin

a=b;

c=b;

end

endcase

4)

always @(b or d) begin

a = b;

c = b;

case (d)

2’b00: a = b >> 1;

2’b11: c = b >> 1;

endcase

end

5)

always@(b or d) begin

case (d) //synopsys full_case

2’b00: a = b >> 1;

2’b11: c = b >> 1;

endcase

end

6)

always@(posedge clk)begin

if(a1)begin

b<=d;

end

else if(a2)begin

c<=d;

end

end

1) 在综合时语句自动补全,补全后就是代码2),因为else后的信号赋值是保持,if...else不完整,所以产生锁存器。

3)属于信号赋值语句不完整,即在d=2’b00时没有对信号c赋值,在d=2’b11时没有对信号a赋值,综合时语句自动补全,明显也出现信号保持,所以产生锁存器。

4)不出现锁存器

5)赋值语句不完整,会产生锁存器

6)缺else,信号赋值语句不全,但属于时序逻辑,不产生锁存器

5、锁存器和触发器综合后Schematic和Device

5.1、触发器

always @(posedge i_clk) begin

if(a)

b<=c;

end

5.2、

always @(*) begin

if(a)

b<=c;

end

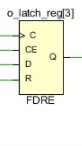

在使用Flip-Flop时,storage element被综合成了FDRE,也就是触发器;当使用Latch电路时,storage element被综合成了LDCE。文章来源:https://uudwc.com/A/BVwZ

有些地方没有时钟,也只能用latch了。比如现在用一个clk接到latch的使能端(假

设是高电平使能),这样需要的setup时间,就是数据在时钟的下降沿之前需要的时

间,但是如果是一个DFF,那么setup时间就是在时钟的上升沿需要的时间。这就说

明如果数据晚于控制信号的情况下,只能用latch,这种情况就是,前面所提到的

latch timing borrow。基本上相当于借了一个高电平时间文章来源地址https://uudwc.com/A/BVwZ