数据采集串口通信系统的Verilog设计与仿真 - 嵌入式

-

简介

在嵌入式系统中,数据采集和串口通信是常见的功能需求。本文将介绍如何使用Verilog语言来设计和仿真一个基于嵌入式系统的数据采集串口通信系统。我们将从系统架构设计开始,逐步实现相关功能,并通过仿真验证设计的正确性。 -

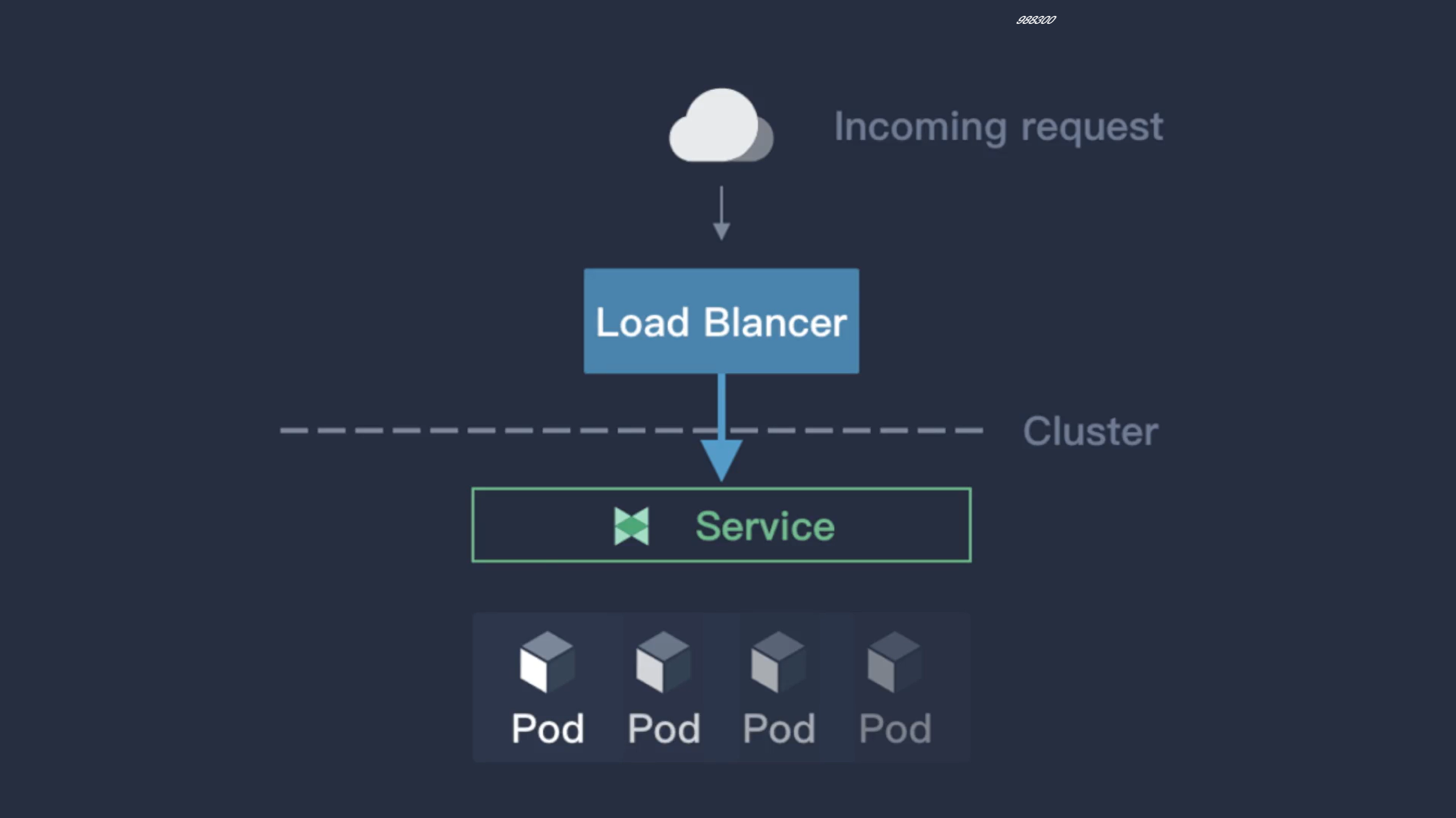

系统架构设计

首先,我们需要确定系统的架构。数据采集串口通信系统一般包括以下主要模块:文章来源:https://uudwc.com/A/BvPEW

- 数据采集模块:用于采集外部传感器或设备的数据。

- 数据处理模块:对采集到的数据进行处理,如滤波、校准等。

- 串口模块:实现与外部设备的串口通信功能,包括发送和接收数据。

- 控制模块:控制整个系统的工作流程和时序。

- 模块设计

3.1 数据采集模块

数据采集模块可以通过模拟输入或者使用开发板上的传感器接口来获取外部数据。这里我们以模拟输入方式为例,假设外部数据是一个8位的模拟量信号。数据采集模块的Verilog代码如下:

module data_collector(

input clk,

input [7:0] analog_input,

output reg [7:0] digital_output

);

always @(posedge clk) begin

// 采集模拟输入数据

digital_output <= analog_input;

end

endmodule

3.2 数据处理模块

数据处理模块可以根据实际需求进行设计,这里我们简单地实现一个数据平均滤波功能。数据处理模块的Verilog代码如下:文章来源地址https://uudwc.com/A/BvPEW