本期主题:

HLS的接口类型定义

往期链接:

- Xilinx HLS基础介绍(一)——HLS概念以及接口管理

目录

- 1.Vitis HLS AXI4 接口概述

- 2.顶层函数的实参类型与接口关系

- 2.1 寄存器接口 S_AXILITE

- 2.2 存储器接口 m_axi

- 2.3 串流接口 axi4_stream

- 1. axi4_stream的工作原理

- 2. axis的结构体

1.Vitis HLS AXI4 接口概述

IP可通过Vitis HLS来生成,IP需要与其他模块通信,一般来说有两种方式:

1.软件控制:通过

寄存器的方式,通过在ARM处理器上运行应用程序,这些程序来访问操作寄存器,从而实现操作IP的目的;

2.自同步:这种模式下,IP将公开所有信号,这些信号用来启动/停止内核,这些信号其他IP和系统的控制;

Vivado IP 流程支持 存储器、串流和寄存器 接口范例,其中每个范例都支持不同接口协议与外部世界进行通信,这些都是AXI4接口,包括:

- 存储器范例 (m_axi):内核通过存储器(如 DDR、HBM、PLRAM/BRAM/URAM)来访问数据;

- 串流范例 (axis):数据从其它串流源(例如,视频处理器或其它内核)串流至内核中,也可从该内核流出;

- 寄存器范例 (s_axilite):内核通过寄存器接口来访问数据,软件则通过寄存器读/写来访问数据;

更为详细的描述如下:

| 范例 | 描述 | 接口类型 |

|---|---|---|

| 存储器 | 内核通过存储器(如 DDR、HBM、PLRAM/BRAM/URAM 支持的接口协议)来访问数据 | ap_memory、BRAM、AXI4 存储器映射 (m_axi) |

| 串流 | 受支持的接口数据将从其它串流源(如视频处理器或其它内核)串流至内核,并且可从内核流出 | ap_fifo, AXI4-Stream (axis) |

| 寄存器 | 内核通过寄存器读取和写入所执行的寄存器接口来访问数据 | ap_none、ap_hs、ap_ack、ap_ovld、ap_vld和 AXI4-Lite 适配器 (s_axilite) |

2.顶层函数的实参类型与接口关系

| C语言实参类型 | 受支持范例 | 默认范例 |

|---|---|---|

| 标量变量(通过值来传递) | 寄存器 | 寄存器 |

| 数组 | 存储器、串流 | 存储器 |

| 指针 | 存储器、串流 、寄存器 | 寄存器 |

| 参考值 | 寄存器 | 寄存器 |

| hls::stream | 串流 | 串流 |

2.1 寄存器接口 S_AXILITE

在vivado IP流程中,默认执行流程是由寄存器来控制IP的。寄存器是通过s_axilite接口,默认的控制协议为 ap_ctrl_hs 。

s_axilite接口可提供下列功能特性:

- 控制协议:采用 块级控制协议 中的块控制协议;

- 标量实参:顶层函数的实参映射到s_axilite接口,ARM可对此寄存器空间执行读/写操作;

- 偏移规则:指定寄存器的偏移地址;

- 捆绑规则:使用s_axilite接口指定多个捆绑,为每个捆绑创建一个独立的接口适配器;

示例code:

#include <stdio.h>

void example(char *a, char *b, char *c)

{

#pragma HLS INTERFACE s_axilite port=a bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=b bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=c bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=return bundle=BUS_A

*c += *a + *b;

}

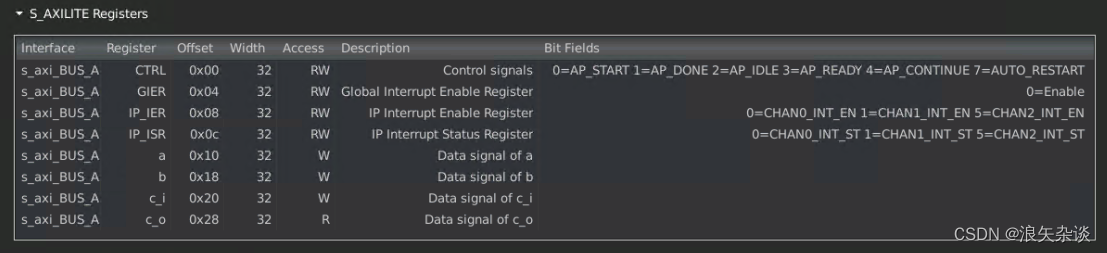

综合结果如下图所示:

- 实参a、b是s_axilite接口,ARM可对此寄存器空间进行写;

- 实参c也是axilite接口,并且有输入、输出的信号;

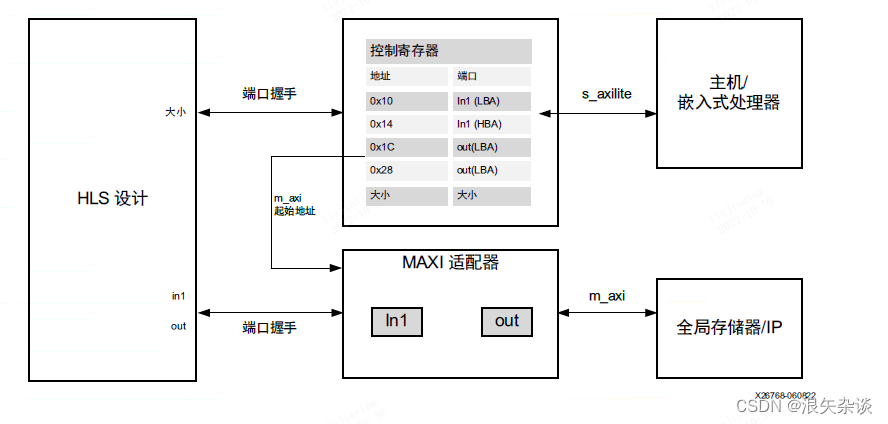

2.2 存储器接口 m_axi

AXI4存储器映射(m_axi)允许内核在全局存储器(DDR、HBM和PLRAM)内读写数据。

看一个例子:

void example(volatile int *a) {

//Port a is assigned to an AXI4 master interface

#pragma HLS INTERFACE mode=m_axi depth=50 port=a

....

}

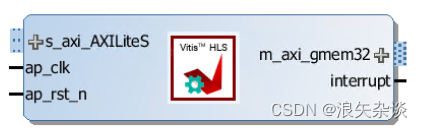

综合出的结果为:

一般来说,axilite会和m_axi组合起来使用,HLS中axilite适合用来去配置寄存器,m_axi适合对全局存储器进行读写执行。

2.3 串流接口 axi4_stream

1. axi4_stream的工作原理

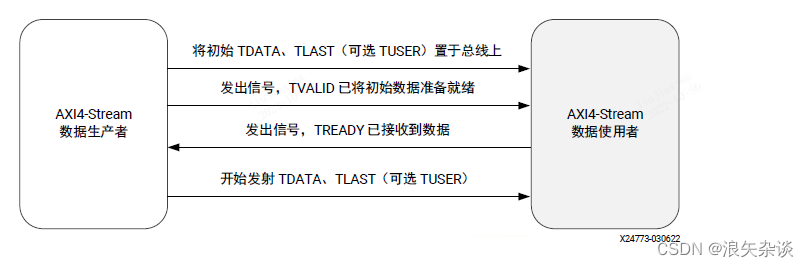

AXI4-Stream 是专为传输任意单向数据而设计的协议。其中:

- TDATA是按照时钟周期来传输的数据;

- TVALID是生产者发出的此时数据有效的信号;

- TREADY是使用者回复的信号,代表此时可以进行数据接收;

- TLAST 信号表明这是串流的最后一个字节;

生产者、使用者的交互图如下:

详细的AXI4-stream的介绍可查看官方文档(UG1307)

2. axis的结构体

如果我们要用vitis_hls中的接口来描述axis,那么就需要通过接口定义TDATA、TVALID、TREADY信号。

AXIS在HLS中的结构体定义如下:

template <typename T, size_t WUser, size_t WId, size_t WDest> struct axis

{ .. };

其中,

- T:代表串流的数据类型

- Wuser:TUSER的信号宽度

- Wid:TID的信号宽度

- Wdest:Tdest信号的宽度

去除了AXI4的旁路元素(即Wuser、Wid、Wdest参数设置为0),这种就是不含旁路的AXI4-stream,也称为hls::stream,这种信号只有数据信息。文章来源:https://uudwc.com/A/Eeya

重点:文章来源地址https://uudwc.com/A/Eeya

- hls::axis、ap_axiu、ap_axis的使用仅限于顶层函数接口,因为它包含着AXI4-STREAM的旁路信息,这种信号无法在内部函数或变量上使用;

对于内部串流,必须使用 hls::stream 信号