番外13:使用ADS进行容差分析(蒙特卡洛分析、灵敏度分析、良率分析、良率优化),以带通滤波器设计为例

资源下载

https://download.csdn.net/download/weixin_44584198/88210327

技术背景

容差分析是当前电子可靠性设计中最先进的技术之一,代表着电子可靠性设计的一个重要发展方向。蒙特卡洛分析是容差分析的一个主要技术。它是分析电路器件在误差情况下,电路性能会不会超过电路性能的规格要求。

简单来说,电路里面的大部分器件器件,比如说电容电阻都会有一定的的误差(比如说5%),但是这些误差的组合会对最终的性能产生怎样的影响呢?众所周知,这是一个小概率问题,但对于成批次、成产量出货的产品,这样的误差是需要被专门分析的,一般大公司或者质量要求高的产品在设计时都会被要求做容差分析,在此介绍使用ADS进行容差分析的方法。

1、设计指标

假设在此我们需要设计一个带通滤波器,滤波器的主要性能指标如下所示:

截止频率1:8MHz

通带1:9.5MHz

通带2:10.5MHz

截止频率2:12MHz

通带波纹:<0.5dB

阻带衰减:>20dB

假设设计使用的集总参数元器件的误差为5%,事实上对于大多数常见的贴片器件,这个5%的误差是非常合理的。

2、带通滤波器设计

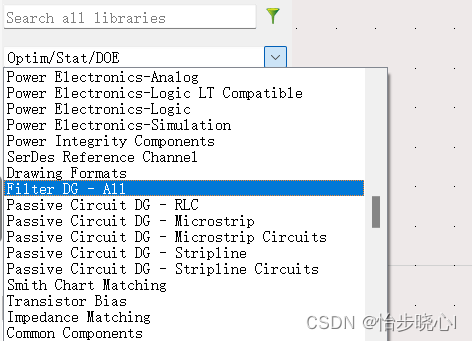

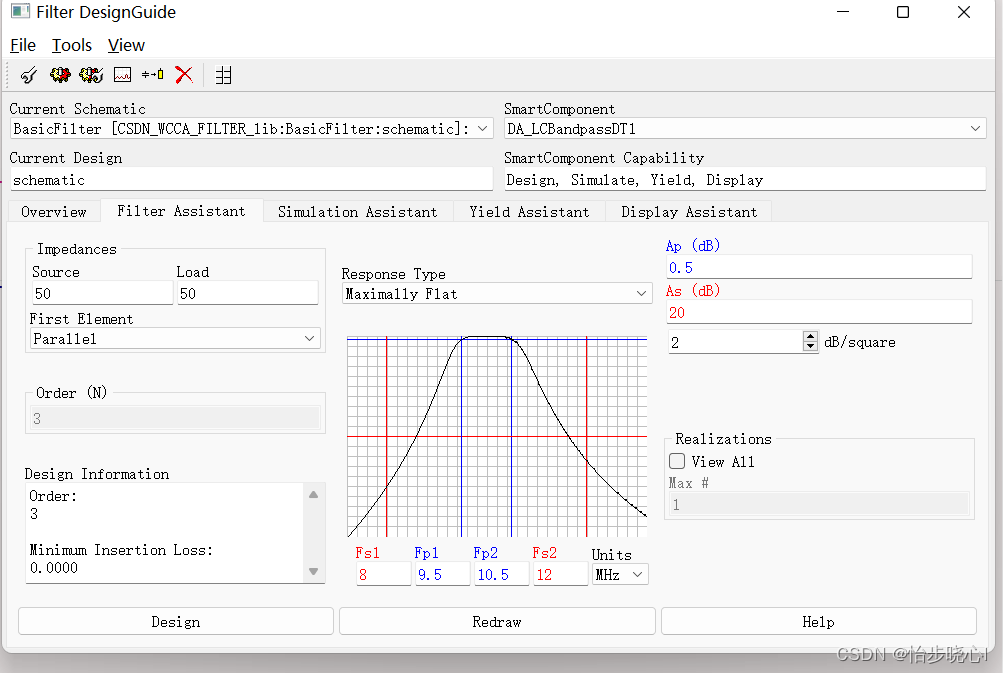

先按照要求设计一个带通滤波器,新建原理图并命名为BasicFilter,在库中找到Filter DG - ALL选项并打开:

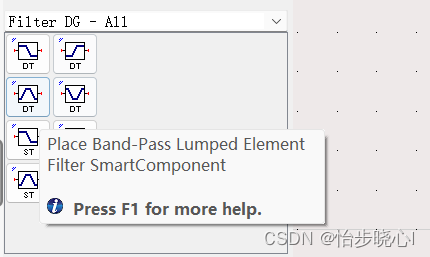

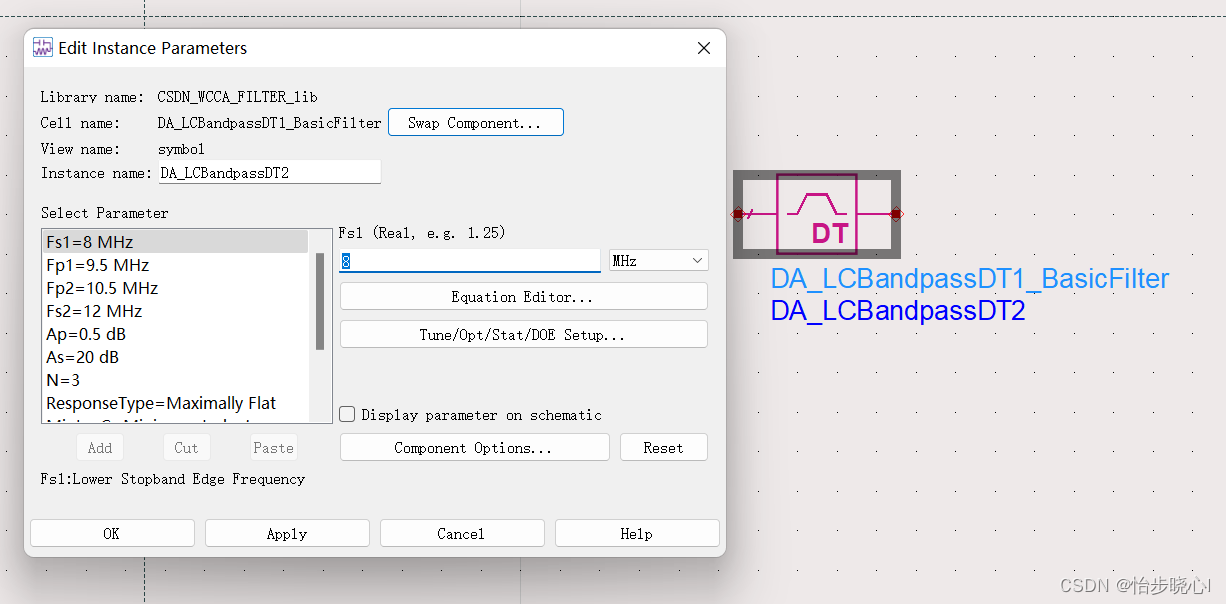

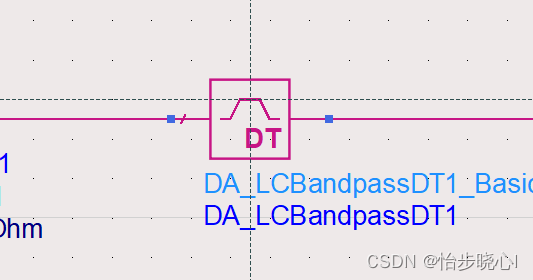

找到其中的带通滤波器设计模组并插入到原理图中(DT):

对于插入后的元器件,合理设置其参数,具体要求按照上面的设计指标来就行:

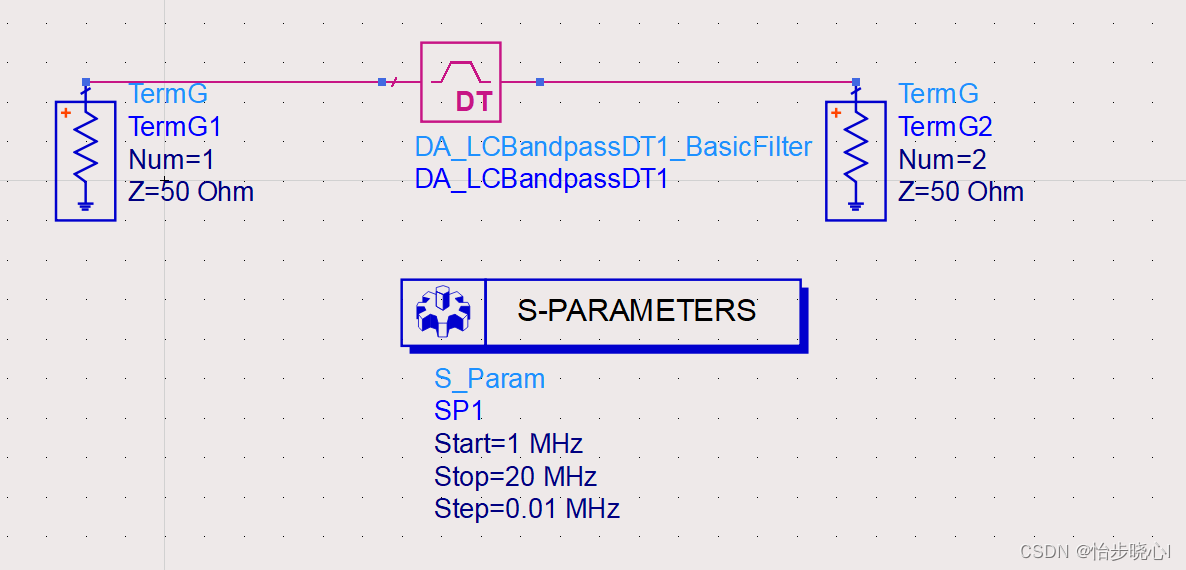

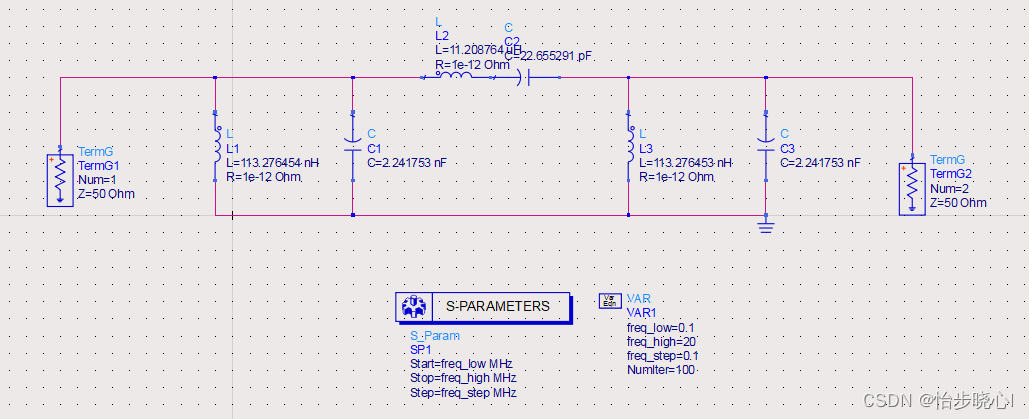

插入相关的仿真控件,主要是S参数控件,并设置其仿真频率:

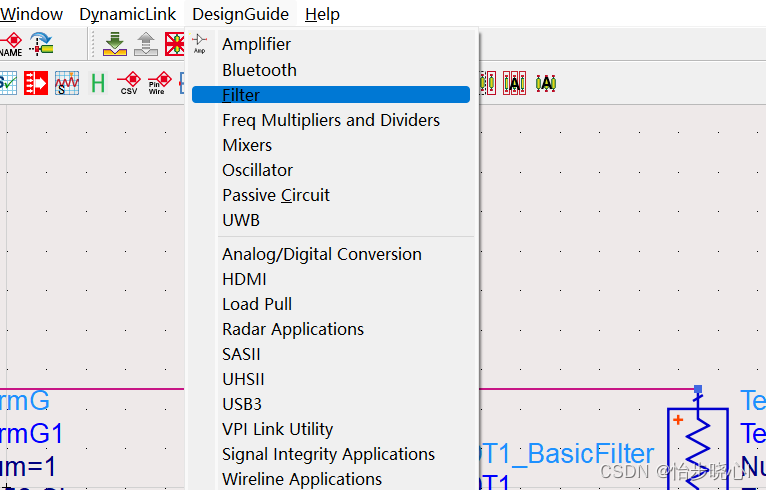

在菜单栏选中DesginGuide,找到Filter选项并打开:

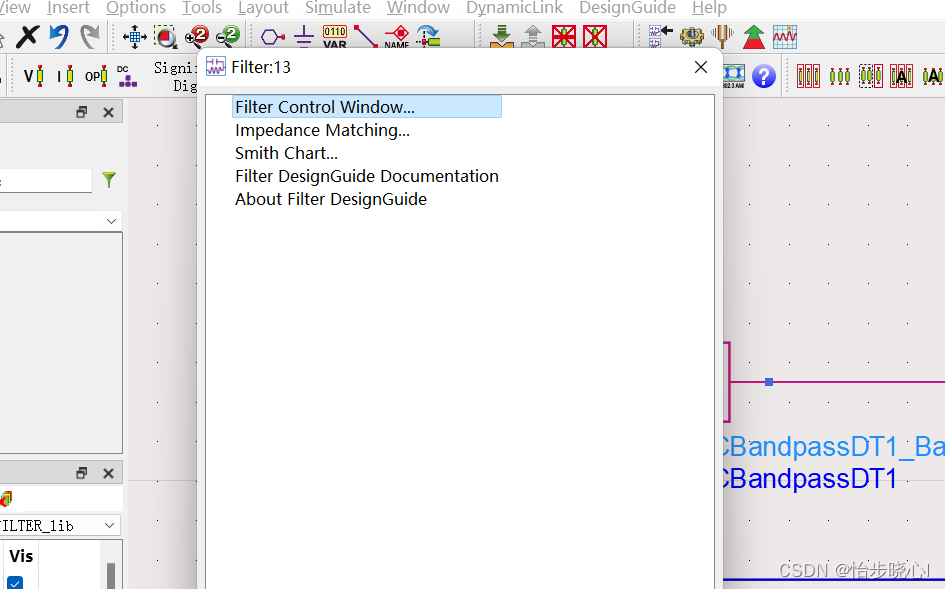

选择第一个Filter Control Window选项,点击OK:

选择第二个选项卡Filter Assistant(默认打开时Overview),点击Design按钮即可:

等待几秒钟后,设计就完成了,虽然表面看不出啥,但是点击按钮深入到器件中查看:

可以发现电路中已经存在相关的电阻电容了:

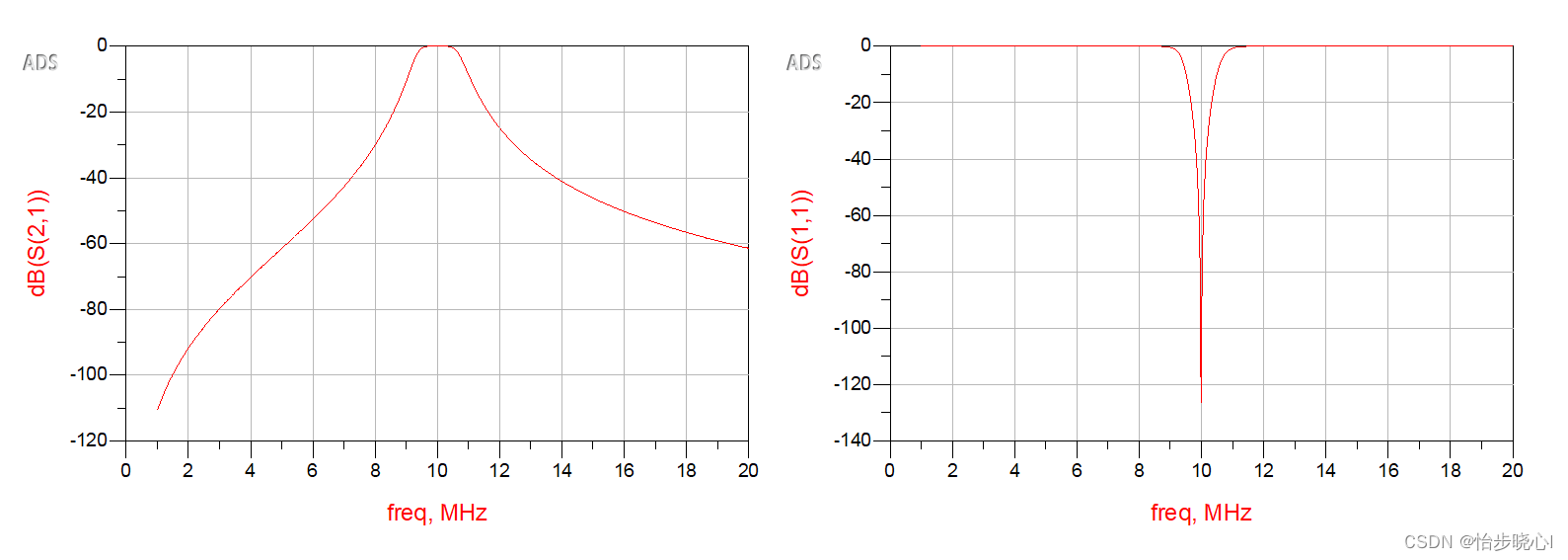

回到上一层点击仿真按钮,可以看到理想情况下的仿真结果如下,性能好像不错:

3、容差分析(此处使用蒙特卡洛分析)

新建一个原理图,命名为MonteCarlo_Filter,将之前设计好的电路放进去并插入相关的S参数控件:

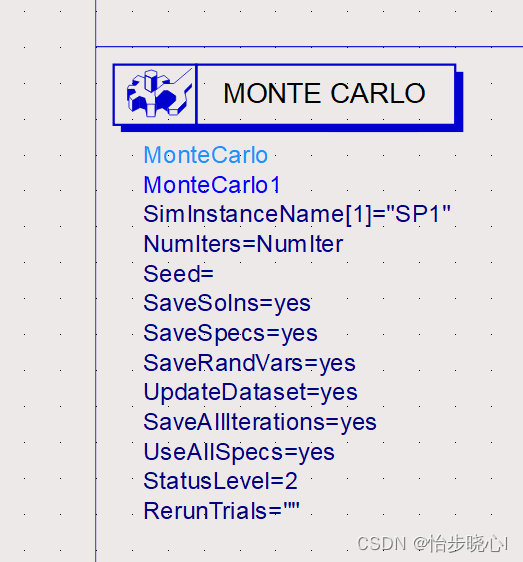

从Optim/Stat/DOE选项中寻找相关的仿真控件(MC,蒙特卡洛缩写),插入后需要设置蒙特卡洛控件的相关参数,如下所示:

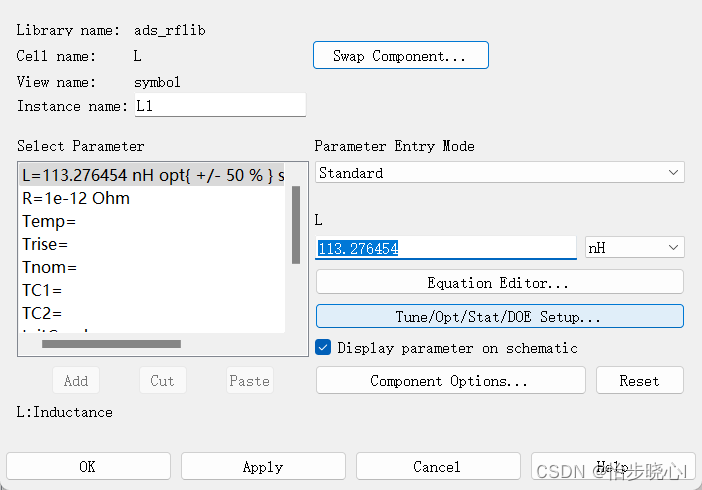

其中Numlter设置成了100,代表一共分析100次,在开始仿真之前,还需要设置器件的误差范围,双击器件并点击Tune/Opt/Stat/DOE Setup按钮:

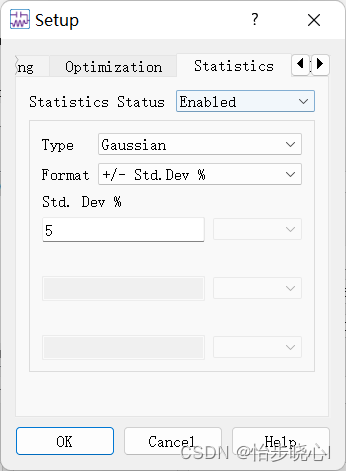

使能Stattistics并设置误差5%:

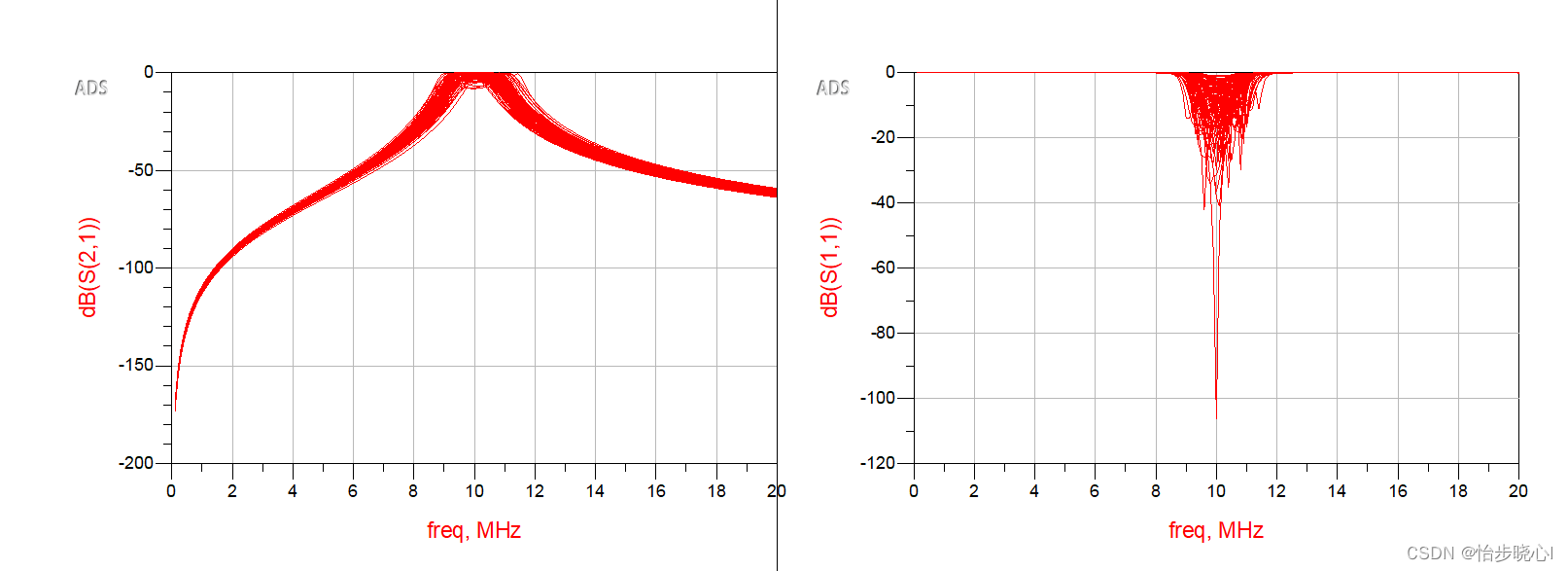

设置完成后点击仿真,查看结果,可见器件误差对电路的最终性能影响较大,频率偏移、匹配性能波动,但是图中看不太清除具体性能:

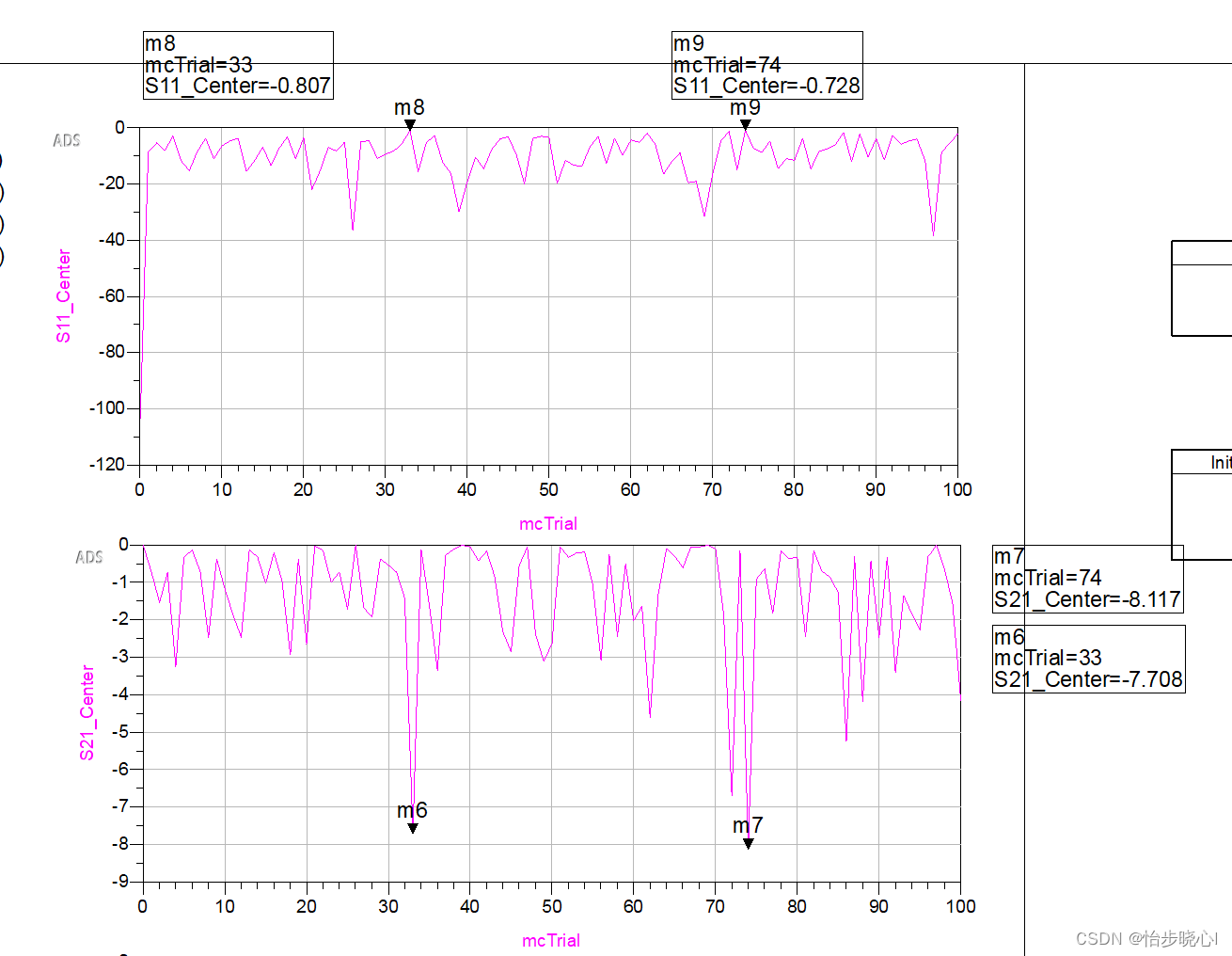

构建如下的观察视窗,观察10MHz时的S11和S21性能,发现蒙特卡洛分析表示在第33次和第74次实验中性能较差,在此时10MHz时的S11大于-1dB,S21小于-6dB,电路功能几乎完全丧失了:

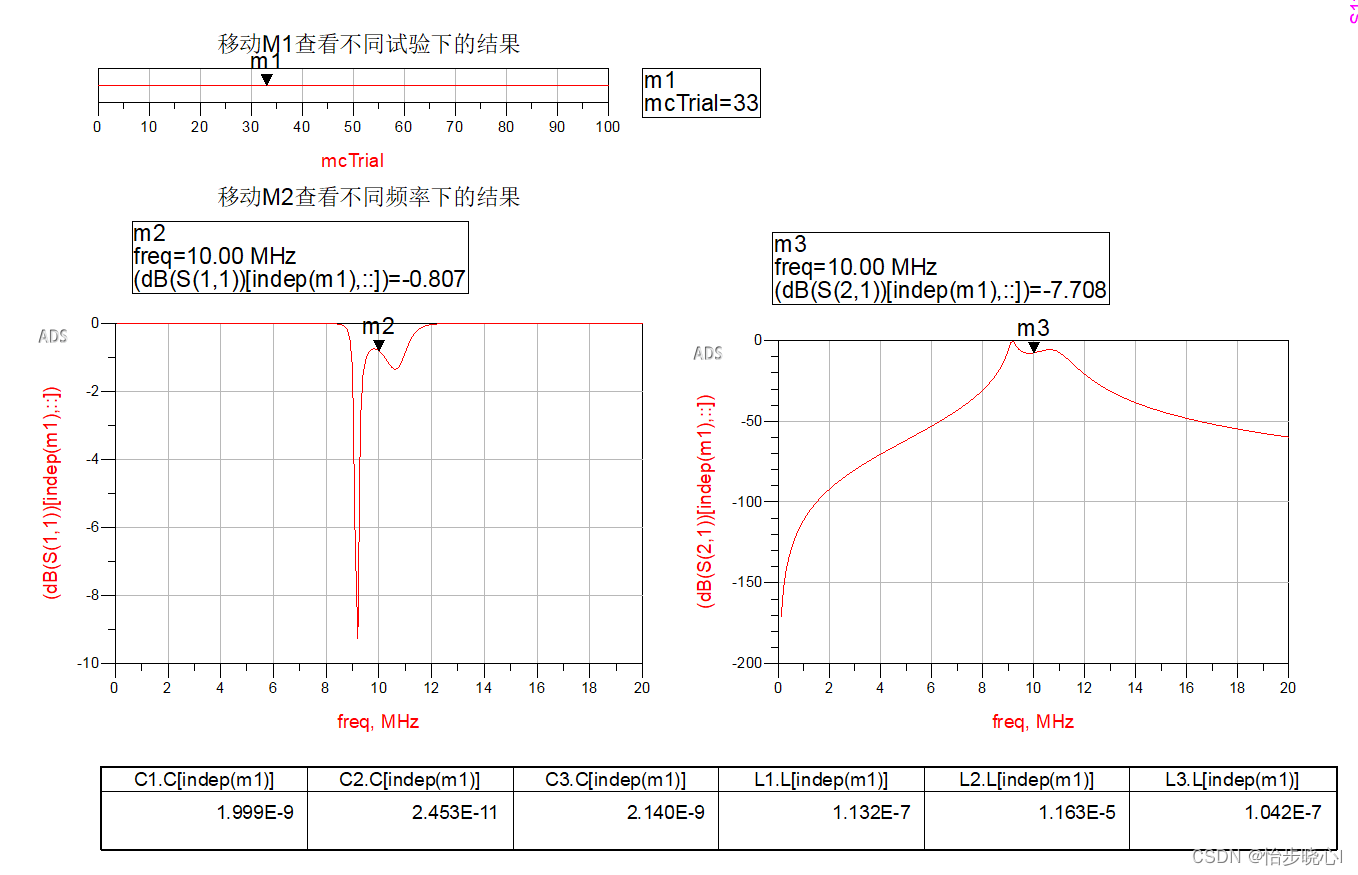

移动鼠标滑钮,查看第33次实验结果和其对应的电阻电容的数值:

可见电路性能在实际的大规模生产时可能问题很大。

4、良率分析与良率优化

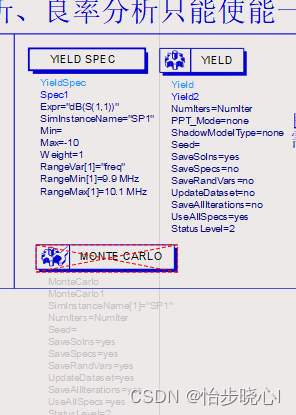

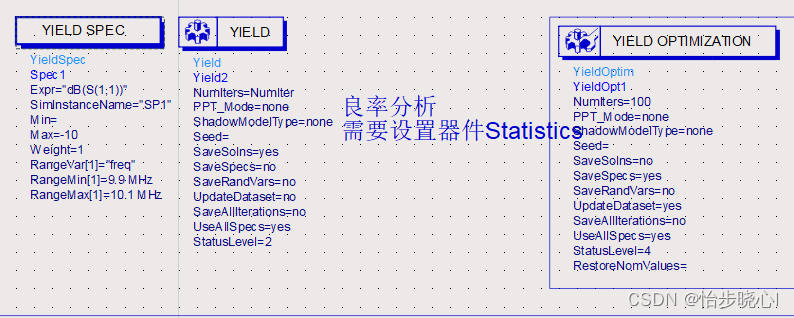

从Optim/Stat/DOE选项中寻找相关的仿真控件(YIELD SPEC和YIELD控件),注意到注释掉原来的蒙特卡洛分析控件,还要合理的设置YIELD SPEC和YIELD控件的数值,观察下面的YIELD SPEC控件,此处设置为在9.96MHz到10.1MHz处S11小于-10dB的器件为良好器件,实际上这个要求已经非常低了:

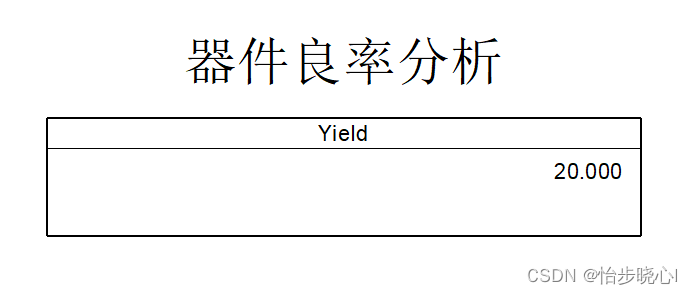

运行仿真,可见在器件误差5%的情况下,整个带通滤波器的良率为20%。这是非常恐怖的,因此在实际设计时应该充分留有余量,比如说我上面的指标,如果将通带范围设置为8MHz到12MHz,器件的S11良率性能可能要好不少:

下面进行良率的优化,从Optim/Stat/DOE选项中寻找相关的仿真控件(YIELD ORTIM…控件),插入后如下所示,可见设置的良率的优化次数为100:

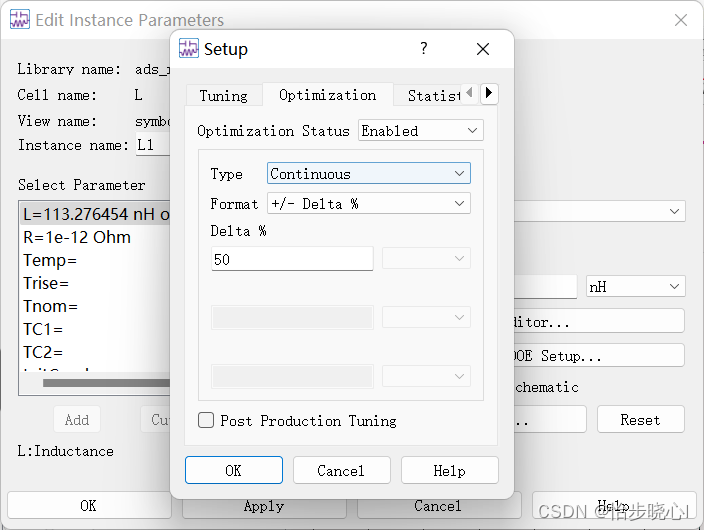

在运行良率优化前,需要设置器件Optim,在此设置器件的优化范围为50%:

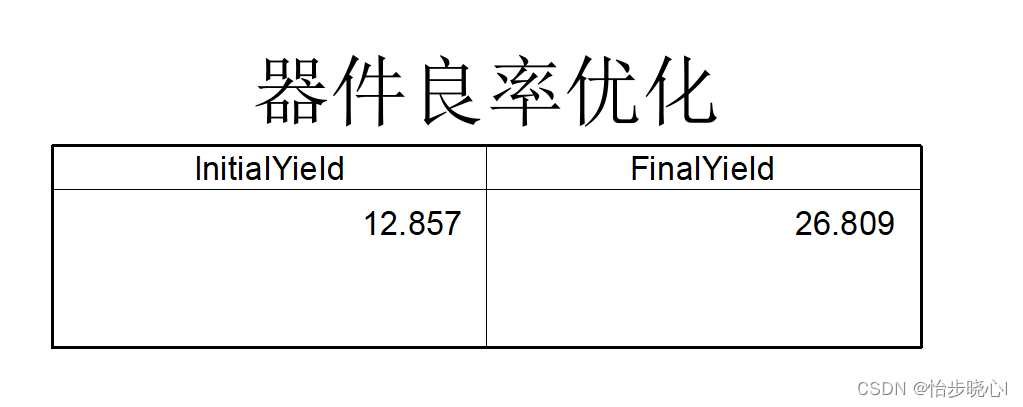

点击仿真运行良率优化,值得注意的是,每次运行良率测试得到的结果可能并不一致,因为实际上这是一种随机实验而已,最终得到的结果,可见初始的良率为12.8%,优化后为27%,这边看似误差比较大,实际上可以通过增大实验次数使其收敛,但是这样运行比较慢,在此就不专门演示了:

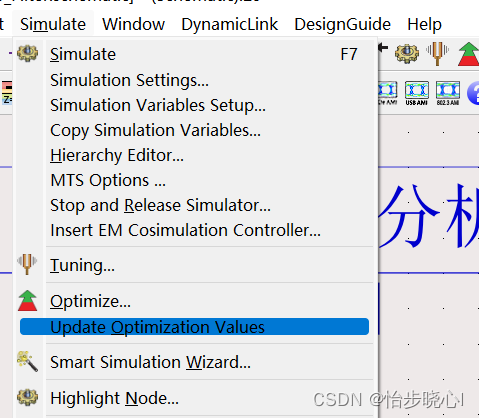

对于优化后的结果,可以在Simulation中的相关选项进行更新,如下所示:

5、灵敏度分析

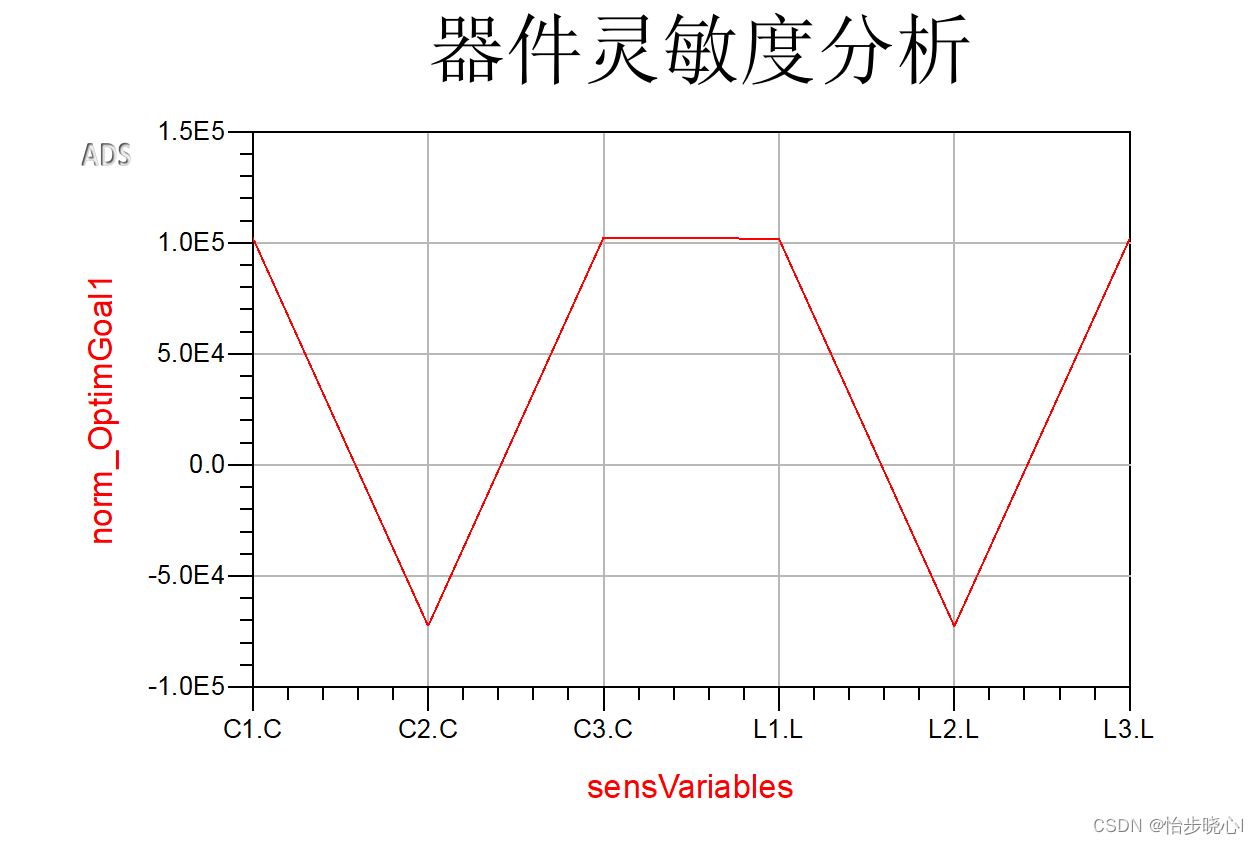

注释掉良率分析相关的控件,从Optim/Stat/DOE选项中寻找相关的灵敏度分析控件,插入和如下所示:

其中Goal需要专门设置,此处测量的是电路在10MHz时S11<-10dB要求下的灵敏度,运行仿真:

可见C1、C3、L1、L3对电路的S11性能贡献较大。文章来源:https://uudwc.com/A/Eyw84

6、结论

设计时留有余量,确保万无一失!文章来源地址https://uudwc.com/A/Eyw84