名称:医院病房呼叫系统病床呼叫

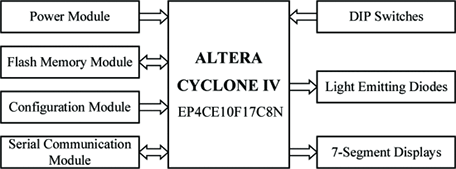

软件:Quartus

语言:Verilog

要求:

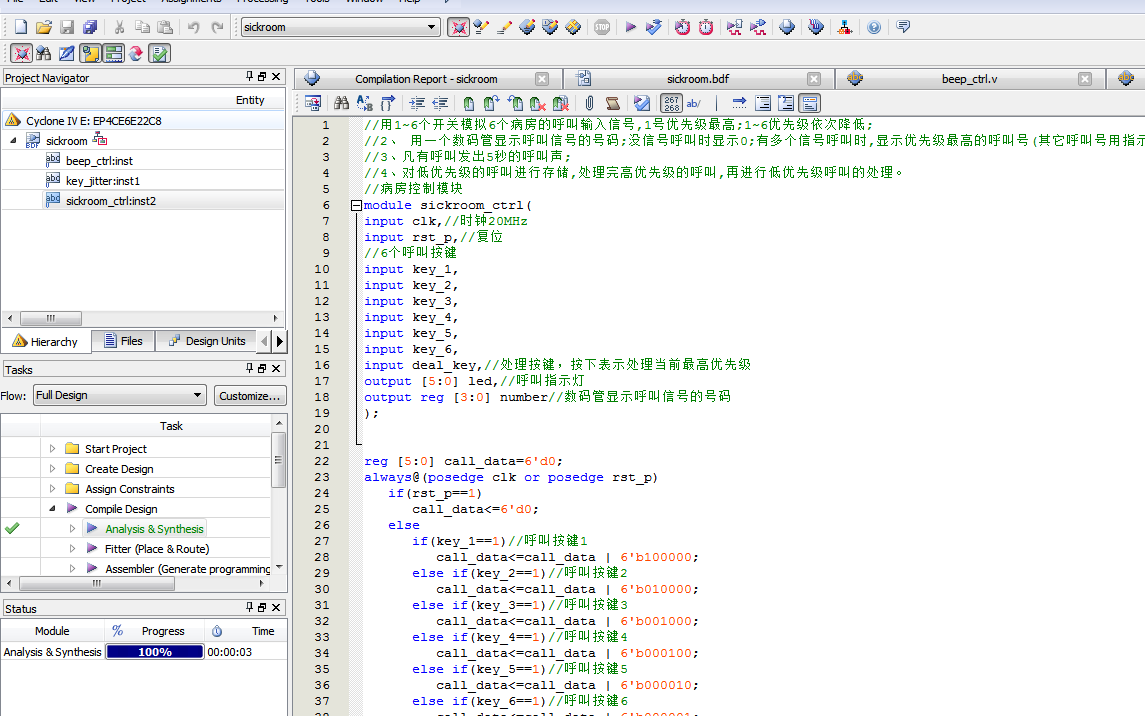

1、用1~6个开关模拟6个病房的呼叫输入信号,1号优先级最高;1~6优先级依次降低;

2、 用一个数码管显示呼叫信号的号码;没信号呼叫时显示0;有多个信号呼叫时,显示优先级最高的呼叫号(其它呼叫号用指示灯显示);

3、凡有呼叫发出5秒的呼叫声;

4、对低优先级的呼叫进行存储,处理完高优先级的呼叫,再进行低优先级呼叫的处理。

代码下载:医院病房呼叫系统数码管显示verilog,quartus_Verilog/VHDL资源下载

代码网:hdlcode.com

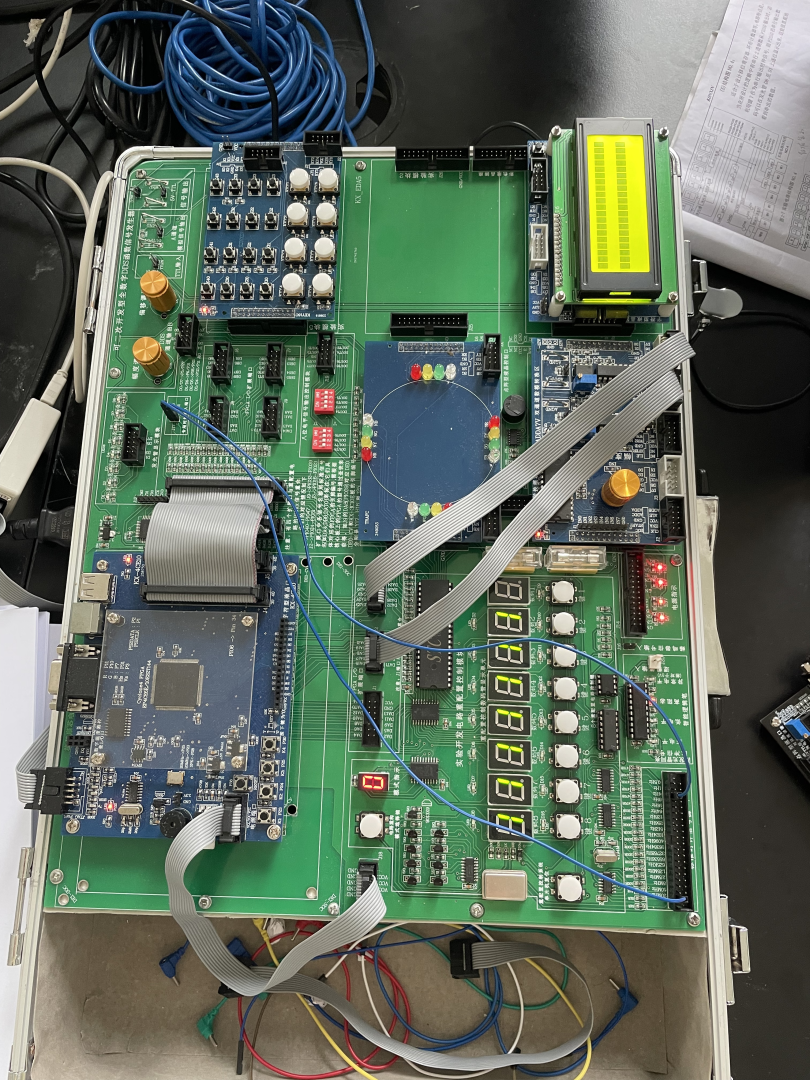

本代码已在实验箱验证,实验箱资料如下:

文章来源地址https://uudwc.com/A/JwO5a

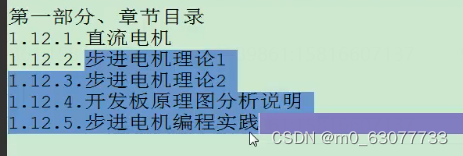

FPGA_CDS讲义1711ok.docx

演示视频:医院病房呼叫系统数码管显示verilog,quartus_Verilog/VHDL资源下载

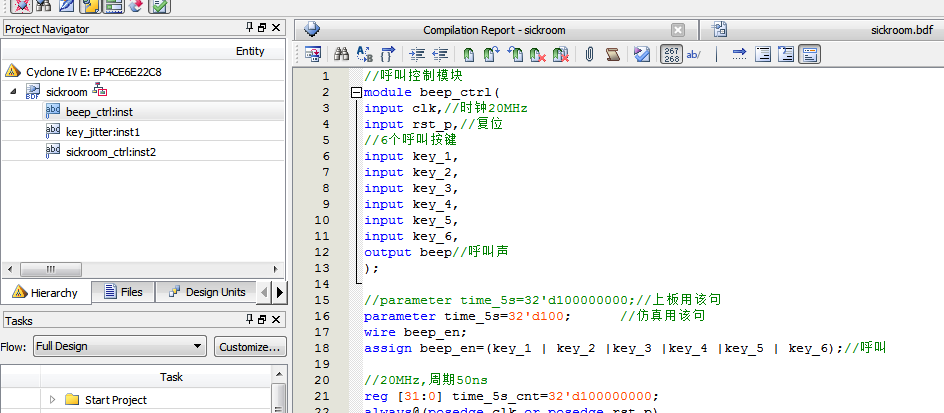

部分代码展示

//用1~6个开关模拟6个病房的呼叫输入信号,1号优先级最高;1~6优先级依次降低; //2、 用一个数码管显示呼叫信号的号码;没信号呼叫时显示0;有多个信号呼叫时,显示优先级最高的呼叫号(其它呼叫号用指示灯显示); //3、凡有呼叫发出5秒的呼叫声; //4、对低优先级的呼叫进行存储,处理完高优先级的呼叫,再进行低优先级呼叫的处理。 module sickroom_ctrl( input clk,//时钟20MHz input rst_p,//复位 //6个呼叫按键 input key_1, input key_2, input key_3, input key_4, input key_5, input key_6, input deal_key,//处理按键,按下表示处理当前最高优先级 output [5:0] led,//呼叫指示灯 output reg [3:0] number//数码管显示呼叫信号的号码 ); reg [5:0] call_data=6'd0; always@(posedge clk or posedge rst_p) if(rst_p==1) call_data<=6'd0; else if(key_1==1)//呼叫按键1 call_data<=call_data | 6'b100000; else if(key_2==1)//呼叫按键2 call_data<=call_data | 6'b010000; else if(key_3==1)//呼叫按键3 call_data<=call_data | 6'b001000; else if(key_4==1)//呼叫按键4 call_data<=call_data | 6'b000100; else if(key_5==1)//呼叫按键5 call_data<=call_data | 6'b000010; else if(key_6==1)//呼叫按键6 call_data<=call_data | 6'b000001;

设计文档(文档可下载):

设计文档.doc

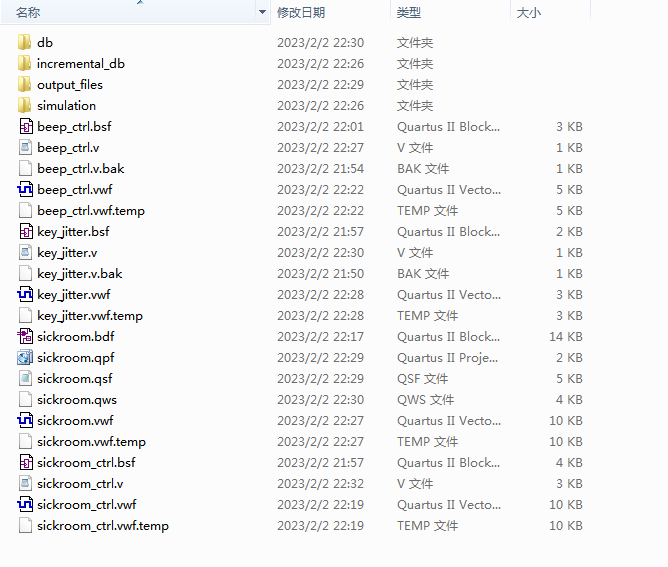

1. 工程文件

2. 程序文件

3. 程序编译

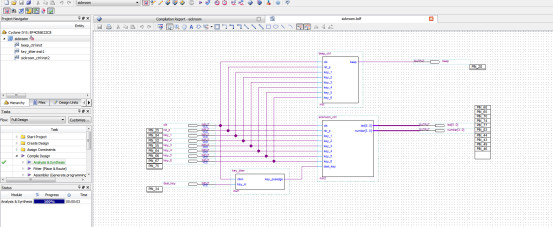

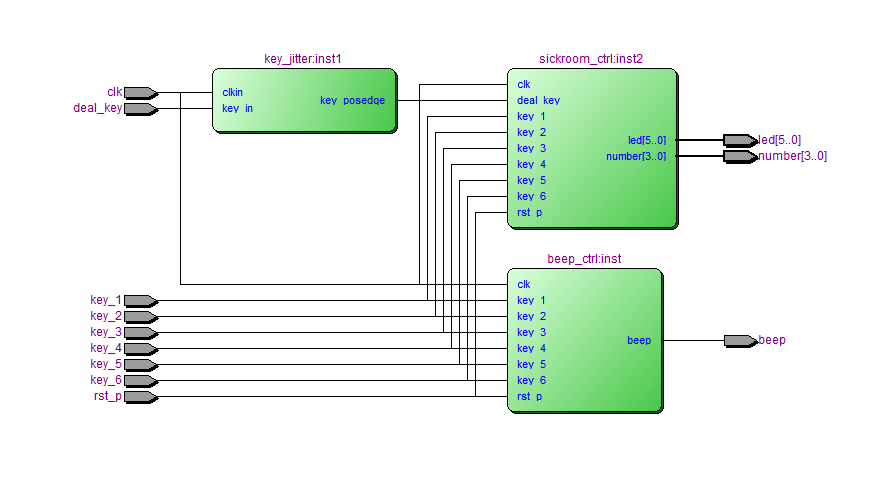

4. RTL图

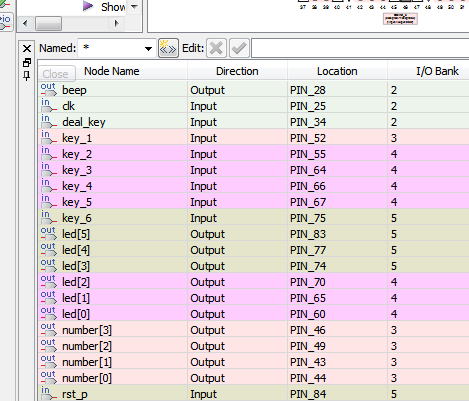

5. 管脚分配

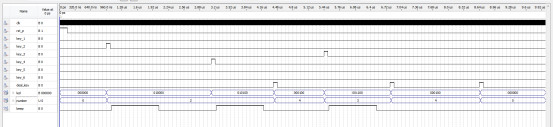

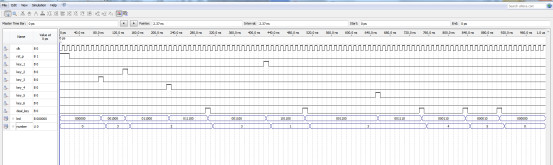

6. 仿真图

整体仿真图

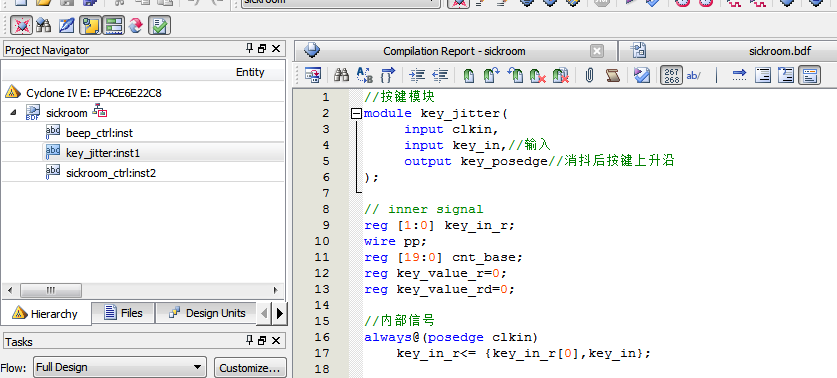

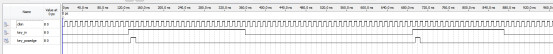

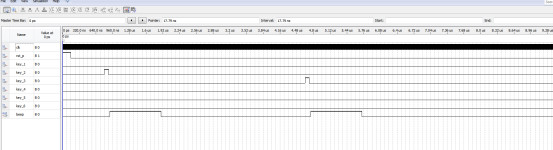

按键模块

病房控制模块

呼叫铃控制模块

文章来源:https://uudwc.com/A/JwO5a

文章来源:https://uudwc.com/A/JwO5a