7系FPGA内部时钟资源整理:

文章来源:https://uudwc.com/A/LakNz

目前,已知的FPGA内部的buf资源分为:

BUFG:直接把时钟信号路由到全局时钟树,可以全芯片使用,驱动能力强,但时钟质量略差,同时资源有限。(优先使用)

BUFH:把时钟信号路由到本时钟域和左右相邻两个时钟域,驱动能力仅次于BUFG,但时钟质量会更好,资源相对丰富(BUFG不够用时做补充使用,内部信号上树首选)

BUFR:只能作用于本时钟域。其余基本和BUFH类似

BUFMR:可以跨越上下两个时钟区域,其余特性和BUFR类似

BUFIO:性能最佳,最适合高速信号,同时作用区域最小,只能作用于本IO BANK区域,适合做高速通信使用,一般搭配IN/OUT FIFO或serdese使用。(有高速需求优先)

......

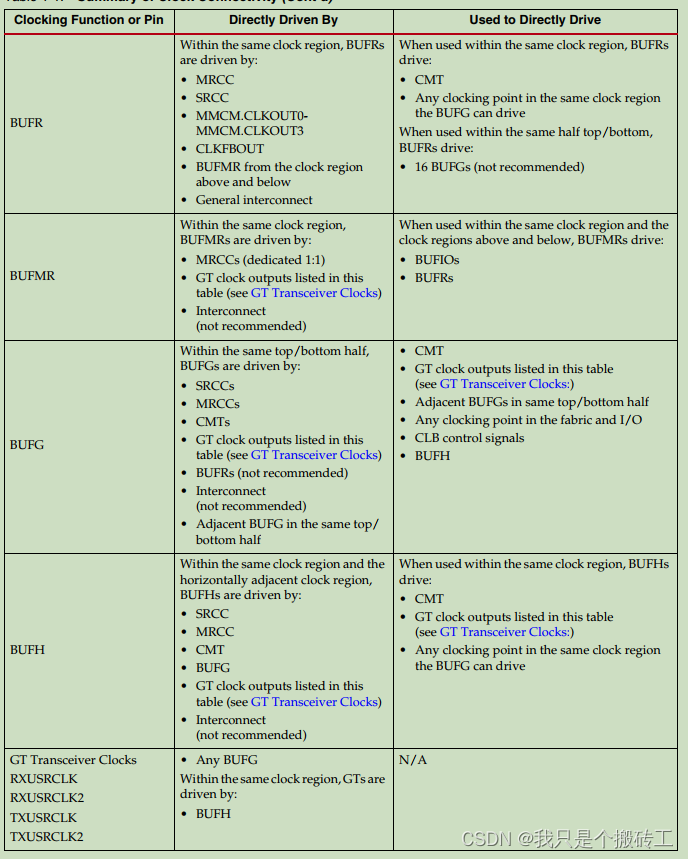

具体的级联和驱动规则,摘录了官方手册ug472 page24

使用BUFIO做时钟的触发器,综合时工具会自动把reg布局在IOB单元,从而实现最靠近PAD(即内部走线最短),适合做高频采样reg,同时实现内部等长走线。(如果不使用BUFIO做时钟,但同时又想把reg靠近IO,可以使用布局约束实现)

eg:

(* IOB = "true" *) reg [3:0] reg_a //即定义reg_a放置在IOB中

如有错误请指正,欢迎继续补充文章来源地址https://uudwc.com/A/LakNz