Burst传输,可以翻译为突发传输或者是连续传输。是指在同一行中相邻的存储单元连续进行数据传输的方式,只要指定起始地址和突发长度(Burst lengths,可以理解为跨度),控制器就会依次自动对后面相同数量的存储单元进行读/写操作,而不需要控制器连续提供列地址

内存相关的知识又是一个大类了,这里只能简单科普。过程大概为:CPU如果要访问读某个存储单元,必须首先给出地址,送入存储器的地址寄存器,然后经译码电路选取相应的存储单元,从存储单元读出的信息要先送入存储器的数据寄存器,在传送给目的部件。如果是写操作,同样是要先把数据放入数据寄存器,在根据给定的地址,写入存储单元中去。

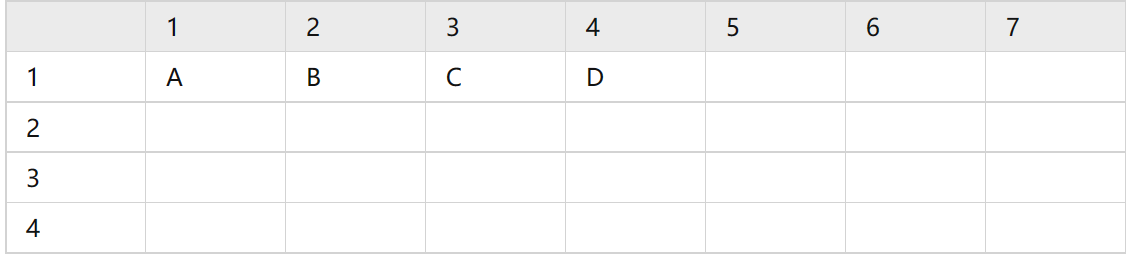

如下面的表格,类似于内存中logic-bank,每一个数据都是用行地址和列地址进行定位的,比如A这个数据,坐标就是第1行第1列。如果CPU要把存储单元第一行的数据读出来,就要给出行地址和列地址,给出行地址以后,为了把整个一行的数据都取出来,就要不断给出列地址和读命令,如果使用Burst模式,就只要给出第一个列地址和突发长度,就能自动读出第一行的每一个数据,可以理解为列地址自动加1,直到把第一列的数据都取出来。这种Burst传输,节省了内存控制资源。文章来源:https://uudwc.com/A/Mx3jL

文章来源地址https://uudwc.com/A/Mx3jL