文章来源地址https://uudwc.com/A/Mxqrg

1.项目简介

基于FPGA的运动目标检测跟踪系统项目,FPGA项目,FPGA图像处理

FPGA项目

采用帧间差分法作为核心算法,该项目涉及图像采集,颜色空间转换,帧间差分核心算法,腐蚀等形态学处理,目标定位,目标标识,图像显示等模块。

通过该项目可以学习到以下两方面内容1.FPGA顶层架构设计、各功能模块详细设计、模块间接口设计:

2.各模块的RTL编写与仿真,在线逻辑分析,程序调试等。

本项目提供完整项目源程序,仿真程序,在线逻辑分析,以及讲解答疑等

2.系统设计及其原理

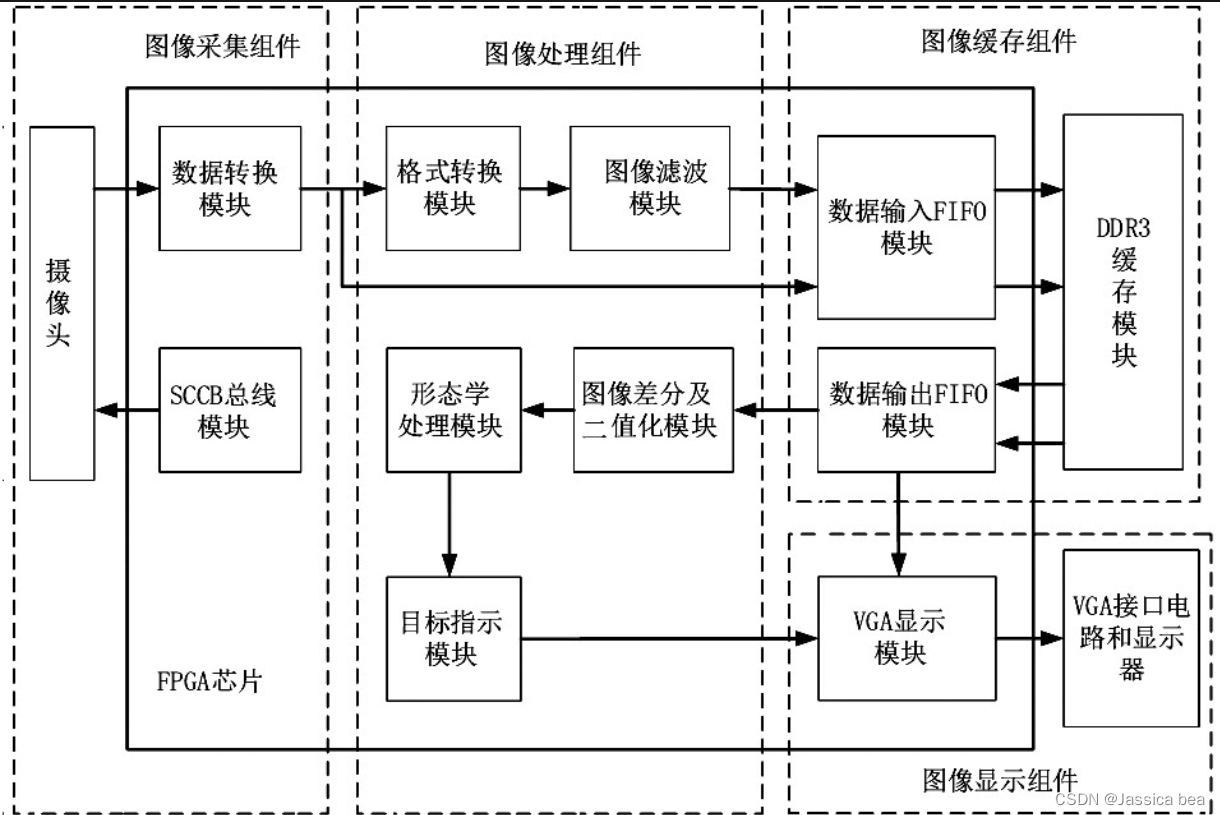

要研究分辨率为640×480和1280×720情况下的彩色视频图像中运动目标的实时检测跟踪技术,首先需要构建一个基于FPGA的测试系统。该系统中应该有较高分辨率的彩色视频输入和输出设备,还应该包含高性能的FPGA芯片和高速数据存储器等。所以,本实验系统的实现按功能划分为图像数据的采集输入、缓存、处理和输出显示四个组件,系统的总体结构框图如图1所示。

图像采集输入组件包括3个模块:OV5640摄像头、相机控制和数据转换。摄像头的选择非常重要,有关采集的一系列设计都是围绕它展开的。由于系统要求能够处理多种分辨率和帧率的RGB彩色图像,此处选用了OmniVision公司生产的OV5640摄像头,它可以满足多种分辨率输入的要求,同时便于图像采集的控制与数据输入。该组件可以通过数字视频接口(DVP)提供30帧/秒最大1080p的彩色高清视频图像,以及能够根据要求输出不同的格式,完全能够达到所述的要求。本系统中采用的格式为RGB565。

在设计过程中,采用串行摄像机控制总线协议(SCCB)对OV5640进行控制。在需要改变所采集图像的分辨率和帧率时,可由SCCB修改摄像头的寄存器地址来实现。

由于OV5640的有效数据位宽为8位,而RGB565图像的像素点是一个16位的二进制数据,所以,一个像素点需要靠两个时钟来完成采集。第一个时钟先采集5位B和6位G的前3位,第二个时钟再采集6位G的后3位和5位的B。完成采集之后,需要一个数据转换模块来读取图像中像素数据并完成数据拼接工作。在FPGA上进行逻辑设计时,根据采集时钟从端口读取数据,再设置一个1位的标志信号作为拼接完成信号即可到像素点的完整数据。

图像数据的缓存组件主要分为输入及输出的先进先出 ( FIFO)模块和第3代双倍数据率同步动态随机存取存储器(DDR3 SDRAM)缓存模块。在对所采集的视频实行一系列的算法处理操作的时候,需要大量的存储空间。而通常FPGA的片上随机存取存储器(RAM)资源有限,因此,需要使用DDR3 作为外部数据缓存模块。然而,当大量的图像数据在FPGA与DDR3之间互相传输时,会产生一些跨时钟的问题,此时,设计读写FIFO模块就很有必要。

虽然DDR3解决了图像数据的缓存问题,但是对其的控制和读写较为复杂,如果只用Verilog HDL来实现的话不仅耗时长,而且不好控制,不能保证质量。在MCB硬核支持下,可以很方便的管理DDR3存储器。

视频图像输入并经过处理后需要直观显示出来判断其检测跟踪的效果,这一任务由图像输出显示组件来完成。该组件由FPGA外部视频图形阵列(Video Graphics Array,VGA)显示器、VGA接口电路以及FPGA内部的VGA驱动模块组成。在对VGA显示模块逻辑设计时,需根据VGA时序标准,用Verilog HDL正确描述行时序和场时序,就能实时地将图像信号输出至VGA接口电路并驱动VGA显示器产生RGB视频图像。

图像采集输入、图像缓存和图像显示三个组件设计实现之后,系统中相关的硬件就可以正确的工作。在系统上电后,采集的视频图像可以通过FPGA存于DDR3中,并通过VGA展示出来。至此,硬件系统平台的搭建工作完成

3.运动目标检测跟踪算法的逻辑设计

实现运动目标的检测跟踪,需要对运动目标的图像进行一系列的处理,如数据格式转换、滤波、二值化、形态学处理、目标指示等。在基于CPU的处理方法中,这些图像处理算法都是十分成熟的[16],但是这些处理都是以帧为单位的,完整的一帧图像数据要先存储到内存里,之后再将其读取出来进行运算。当视频图像的分辨率较高(如640×480)且帧率较高(如30帧/秒)时,基于CPU处理方式的PC平台上无法进行实时处理。这时必须使用具有强大并行处理能力的硬件进行加速,才可能进行实时的运动目标检测跟踪,FPGA就是这类新兴的加速处理硬件。

但用FPGA进行处理时,并不是所有的软件算法都能在FPGA上实现,而是要选用合适的算法,再根据FPGA可并行流水线处理的特点及其内部资源的限制,用HDL重新进行数据的组织和处理行为的描述,才能得到能够用于FPGA实现的运动目标检测跟踪算法,从而达到实时处理的目的。在FPGA内部,又可以分解为多个模块,每个模块都对应一个特定的处理算法。

3.1格式转换算法

格式转换算法的设计是为了实现彩色图到灰度图的变换。

图像格式转换包括两个步骤:一是单纯性格式转换,另一是图像数据转换。单纯性格式转换是为后续计算方便引入的,就是要把16位(RGB565)的图像数据转换成24位(RGB888)。转换的方法是:原数填充,低位补充,即{{R[4∶0],R[2∶0]},{G[5∶0],G[1∶0]},{B[4∶0],B[2∶0]}}。

图像数据转换则是为了减少计算量的同时便于后续算法的实现引入的,也就是从24位真彩色图像(RGB888)转换成8位的灰度图像。彩色到灰度的转换方法和公式有很多,但有些并不适合FPGA实现,这里选择如文献[17]中的方法表示为(亮度信号Y作为图像灰度数据)

式中,R、G、B表示的是RGB888中的红、绿、蓝信号;而Y、Cb、Cr则代表YUV中的亮度、色调、饱和度。

3.2灰度图像滤波处理

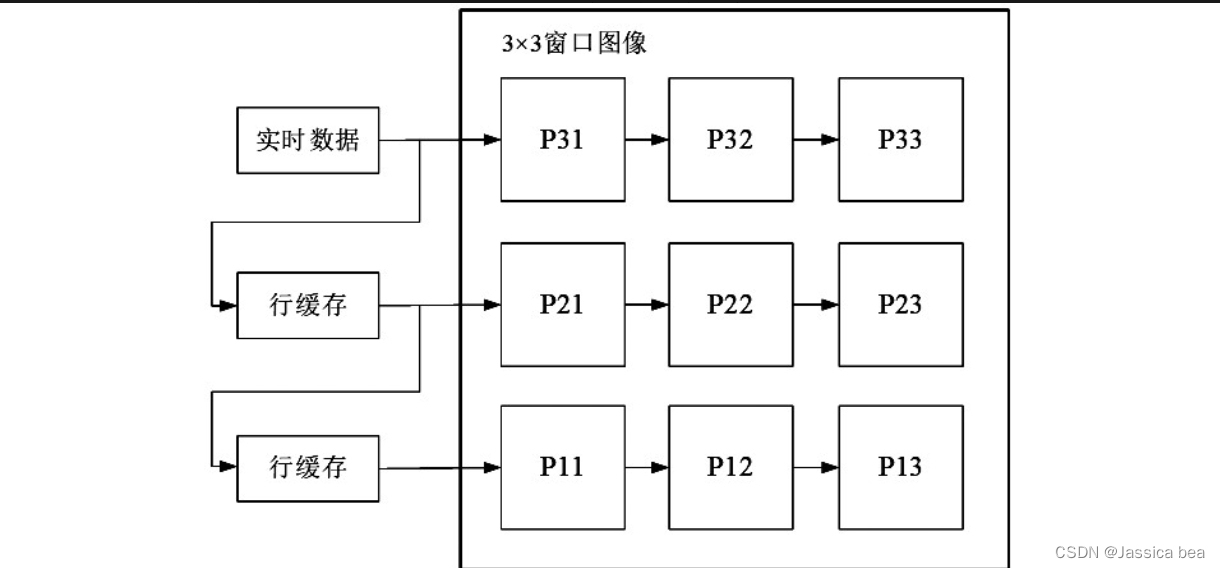

在FPGA中实现滤波算法的逻辑设计时,采用流水线操作方法,用面积换速度,从而到达实时的效果。第一级流水线先对每行的三个像素值进行相加,第二级再对第一级得到三个数进行求和,第三级计算这9个像素值的算术平均值。这里不直接对求和结果进行除运算,而是使用多次移位的方法来代替。 在FPGA逻辑设计时,采用两个行缓存暂存前两行数据,如图所示。用9个点的像素值之和的算术平均值替换中心点P22的值,就实现了3×3的均值滤波。

4.设计验证

更多FPGA图像处理算法实现的项目(经过验证)。其中包括

1.颜色空间转换

2.快速中值滤波算法

3.sobel边缘检测算法

4.OTSU (最大类间方差)算法

5.卡尔曼滤波算法

6.局部自适应分割算法

7.目标检测与跟踪算法

8.图像增强去雾算法文章来源:https://uudwc.com/A/Mxqrg