文章目录

- 简介

- Verilog HDL

- Iverilog

- Gtkwave

- 环境搭建

- 软件的安装

- Vim 之 Verilog 语法高亮配置

- 简单的计数器示例

- 计数器程序的编写

- 仿真测试

简介

Verilog HDL

Verilog HDL 是一种用于设计数字电路的硬件描述语言,它可以用来描述数字电路的功能和结构,并且可以被编译器转换成可以在现实世界中运行的电路。

Verilog HDL语言 由一系列的关键字、表达式和语句组成,这些元素可以用来描述电路的输入、输出和内部状态。

Iverilog

Iverilog 是一种基于 Verilog HDL 的综合工具,用于将 Verilog HDL代码 转换成可以在现实世界中运行的硬件电路。Iverilog 使用一种叫做 ”门级综合” 的技术来生成电路模型,它可以将 Verilog HDL代码 转换成门级电路模型,也可以将其转换成可以在 FPGA 或其他硬件平台上运行的实际电路。

Iverilog 还提供了一些其他的功能(例如:模拟和验证电路的功能以及自动化测试平台的集成等),这些功能使得 Iverilog 成为数字电路设计领域的一种非常有用的工具。

Gtkwave

Gtkwave 是 Xilinx 公司开发的一种用于设计和验证 GTX(通用图形处理器)的工具,同时也可以用于 iverilog 仿真和查看仿真波形。它提供了一个简单易用的界面,可以帮助用户快速设计和验证 GTX 芯片,并可以自动生成用于 FPGA 或 ASIC 实现的代码。它还支持多种硬件描述语言,如 Verilog HDL、VHDL 等,方便用户将设计转换为可实现的硬件电路。

运用 gtkwave 软件进行 iverilog 仿真时,用户可以设置仿真参数,如仿真时间、仿真精度等,并可以选择不同的模块进行仿真。仿真结果会以波形的形式显示在软件界面上,用户可以通过调整波形的显示方式和参数来更好地观察和理解仿真结果。同时,gtkwave 软件还提供了多种工具,如波形缩放、标记、测量等,帮助用户更方便地分析和验证设计。

环境搭建

软件的安装

(1)Iverilog 的安装

- 在 Linux 系统下,打开终端并执行以下命令进行安装。

sudo apt-get install iverilog

- 安装成功后,执行

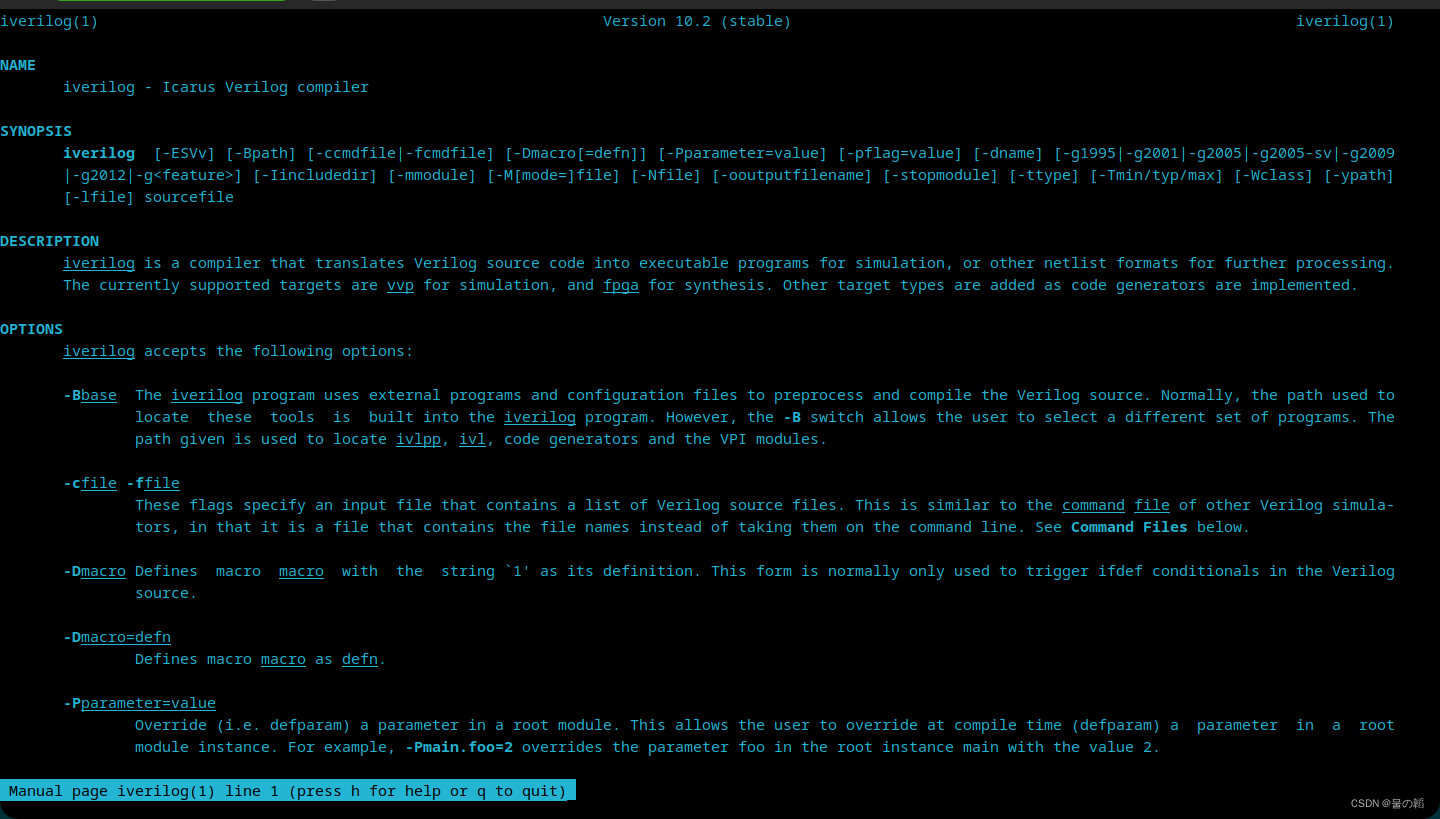

man iverilog命令可以查看 iverilog 软件的使用方法,如下图所示。

注:安装 ivreilog 软件的同时会安装

vpp软件,该软件是 Verilog 的仿真软件。

(2)GTKWave 的安装

- 在 Linux 系统下,打开终端并执行以下命令进行安装。

sudo apt-get install gtkwave

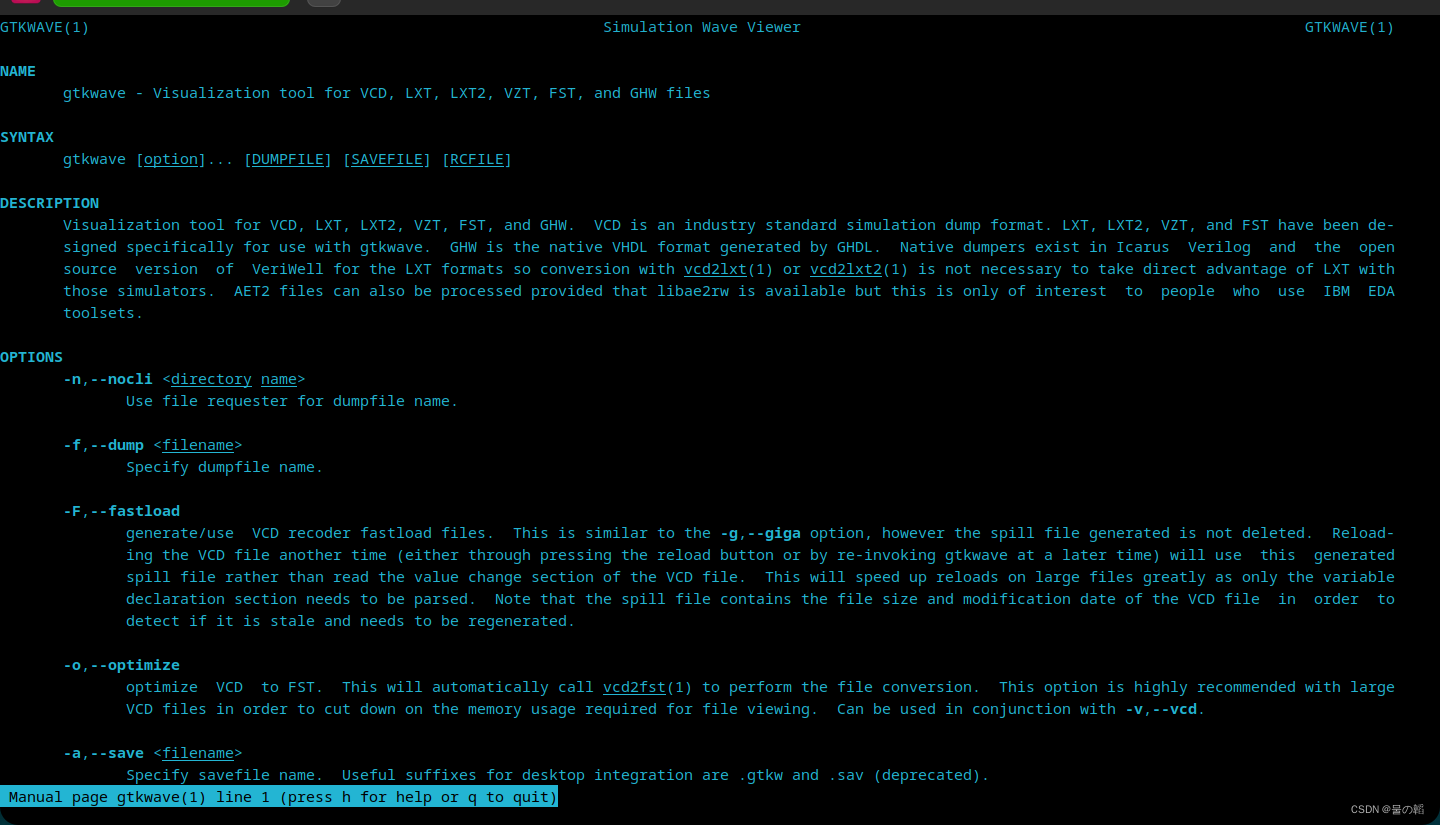

- 安装成功后,执行

man iverilog命令可以查看 gtkwave 软件的使用方法,如下图所示。

注:gtkwave 是一款功能强大的 GTX 设计和验证工具,同时也是 iverilog 仿真和波形查看的有力工具,为用户提供了方便、高效的设计和验证环境。

Vim 之 Verilog 语法高亮配置

(1)基本配置

- 打开 Linux 终端,执行以下命令对 VIM 进行配置。

vim ~/.vimrc

- 编辑

.vimrc文件,添加以下内容并保存退出。

set nocompatible "不兼容vi

syntax on "语法高亮度显示

set noerrorbells " 不让vim发出讨厌的滴滴声

set shortmess=atI " 启动的时候不显示那个援助索马里儿童的提示

set t_Co=256 "开启256色支持

set hlsearch "搜索设置高亮

colorscheme desert "配色方案

set background=dark "配置主题整体的色调,只有两个选择:dark和light(暗色调和亮色调)

highlight Function cterm=bold,underline ctermbg=red ctermfg=green "color set

set nu "显示行号

set relativenumber "显示相对行号

set cursorcolumn "add cursor in column

set cursorline "add cursor in line

"set guifont=Monospace\ 16 "gui style

set guifont=Courier_new:h16

set lines=35 columns=118 "其中lines是窗口显示的行数,columns是窗口显示的列数

winpos 200 100 "后面两个参数指的自屏幕左上角像素值参考位置

set tabstop=4 "tab键相当于4个空格键

set expandtab "來將 tab 转成 space combine with tabstop

set shiftwidth=4 "换行自动变为空格

set autoindent "设置自动缩进 自动缩进,当你第一行敲 tab + 文字 回车后 下一行自动给你加个 tab

set backspace=2 "enable backspace

set novisualbell "不要闪烁

set laststatus=2 "启动显示状态行

set encoding=utf-8 "文件编码

inoremap ( ()<ESC>i

inoremap [ []<ESC>i

"ban up and also keys

imap <Up> <Nop>

imap <Down> <Nop>

imap <Left> <Nop>

imap <Right> <Nop>

nmap <Up> <Nop>

nmap <Down> <Nop>

nmap <Left> <Nop>

nmap <Right> <Nop>

imap jk <Esc> "在编辑模式下使用jk替代ESC进入命令模式

nmap ,l ^

nmap ,r $

"进行版权声明的设置

"添加或更新头

map <F3> :call TitleDet()<cr>'s

function AddTitle()

call append(0,"/*=============================================================================")

call append(1,"#")

call append(2,"# Author: meng - email@vip.qq.com")

call append(3,"#")

call append(4,"# QQ : xxxxxxxxx ")

call append(5,"#")

call append(6,"# Last modified: ".strftime("%Y-%m-%d %H:%M"))

call append(7,"#")

call append(8,"# Filename: ".expand("%:t"))

call append(9,"#")

call append(10,"# Description: ")

call append(11,"#")

call append(12,"=============================================================================*/")

echohl WarningMsg | echo "Successful in adding the copyright." | echohl None

endf

"更新最近修改时间和文件名

function UpdateTitle()

normal m'

execute '/# *Last modified:/s@:.*$@\=strftime(":\t%Y-%m-%d %H:%M")@'

normal ''

normal mk

execute '/# *Filename:/s@:.*$@\=":\t\t".expand("%:t")@'

execute "noh"

normal 'k

echohl WarningMsg | echo "Successful in updating the copy right." | echohl None

endfunction

"判断前10行代码里面,是否有Last modified这个单词,

"如果没有的话,代表没有添加过作者信息,需要新添加;

"如果有的话,那么只需要更新即可

function TitleDet()

let n=1

"默认为添加

while n < 10

let line = getline(n)

if line =~ '^\#\s*\S*Last\smodified:\S*.*$'

call UpdateTitle()

return

endif

let n = n + 1

endwhile

call AddTitle()

endfunction

(2)加载高亮文本

- 在 Linux 系统的家目录下的

.vim文件夹中新建 syntax 和 ftdelect 文件夹,依次执行以下命令。

mkdir ~/.vim/ftdelect

mkdir ~/.vim/syntax

- 在 ftdelect 目录下新建一个名为

sv.vim的文本文件,并编辑添加以下内容。

au BufReaad,BufNewFile *.sv set filetype=systemverilog

- 下载 Verilog 语法高亮文件,下载后重命名为

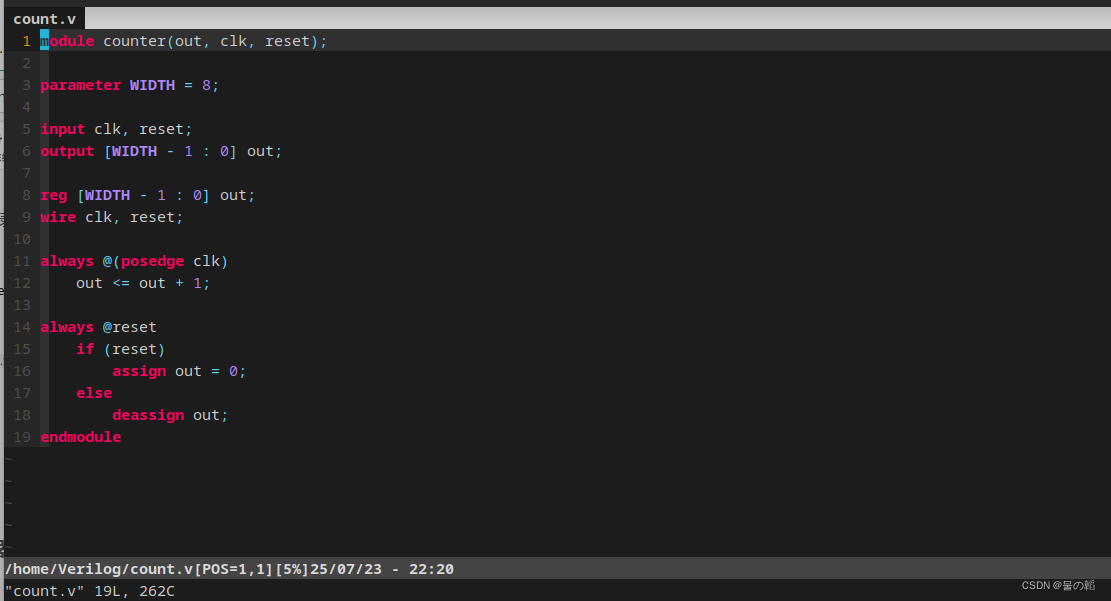

systemverilog.vim,并放入到 syntax 目录下,重启 VIM 后便配置成功,效果如下图所示。

简单的计数器示例

计数器程序的编写

(1)在任意目录下,创建一个名为 count.v 的仿真文件,并编写 Verilog HDL 计数器程序,该程序的具体内容如下。

module counter(out, clk, reset);

parameter WIDTH = 8;

input clk, reset;

output [WIDTH - 1 : 0] out;

reg [WIDTH - 1 : 0] out;

wire clk, reset;

always @(posedge clk)

out <= out + 1;

always @reset

if (reset)

assign out = 0;

else

deassign out;

endmodule

(2)创建一个名为 sim_count.v 的测试文件,并编写 testbench,该 testbench 的内容如下所示。

`timescale 1ns/1ns

module sim_count;

reg reset = 0;

initial

begin

#17 reset = 1;

#11 reset = 0;

#29 reset = 1;

#11 reset = 0;

#250 $stop;

end

reg clk = 0;

always #5 clk = !clk;

wire [7 : 0] value;

counter cqupthao(value, clk, reset);

initial

$monitor("When time is %t (ns), value = %h (%0d)" , $time, value, value);

initial

begin

$dumpfile("sim_count.vcd");

$dumpvars(0, sim_count);

end

endmodule

其中,

$dumpfile("sim_count.vcd")中的sim_count.vcd为指定存储的文件名,$dumpvars(0, sim_count)中的 sim_count 为模块名。

仿真测试

- 方式一

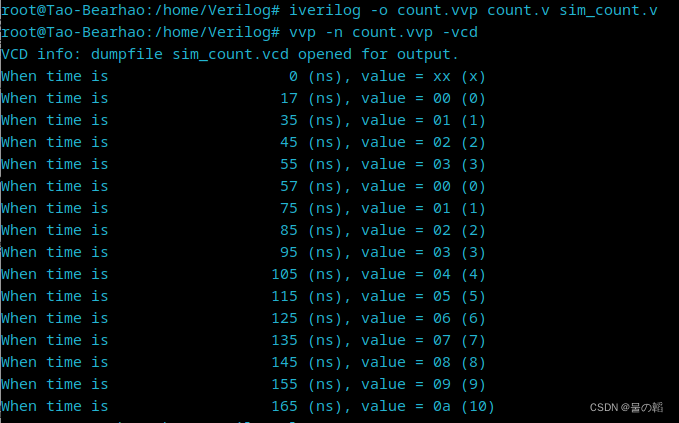

(1)将以上的仿真文件 count.v 和测试文件 sim_count.v 打包成一个 vvp 文件,在 Linux 终端执行以下命令。

iverilog -o count.vvp count.v sim_count.v

(2)将打包成的 vvp 文件转换为 vcd 文件提供给 gtkwave 软件使用,在终端中执行以下命令。

vvp -n count.vvp -vcd

正确运行以上命令后,会输出如下图所示的结果。

注意:此刻,该项目的目录下有

count.v count.vvp sim_count.v sim_count.vcd四个文件。

(3)成功转换文件之后将此文件导入 gtkwave 软件中,在终端中执行以下命令。

gtkwave sim_count.vcd

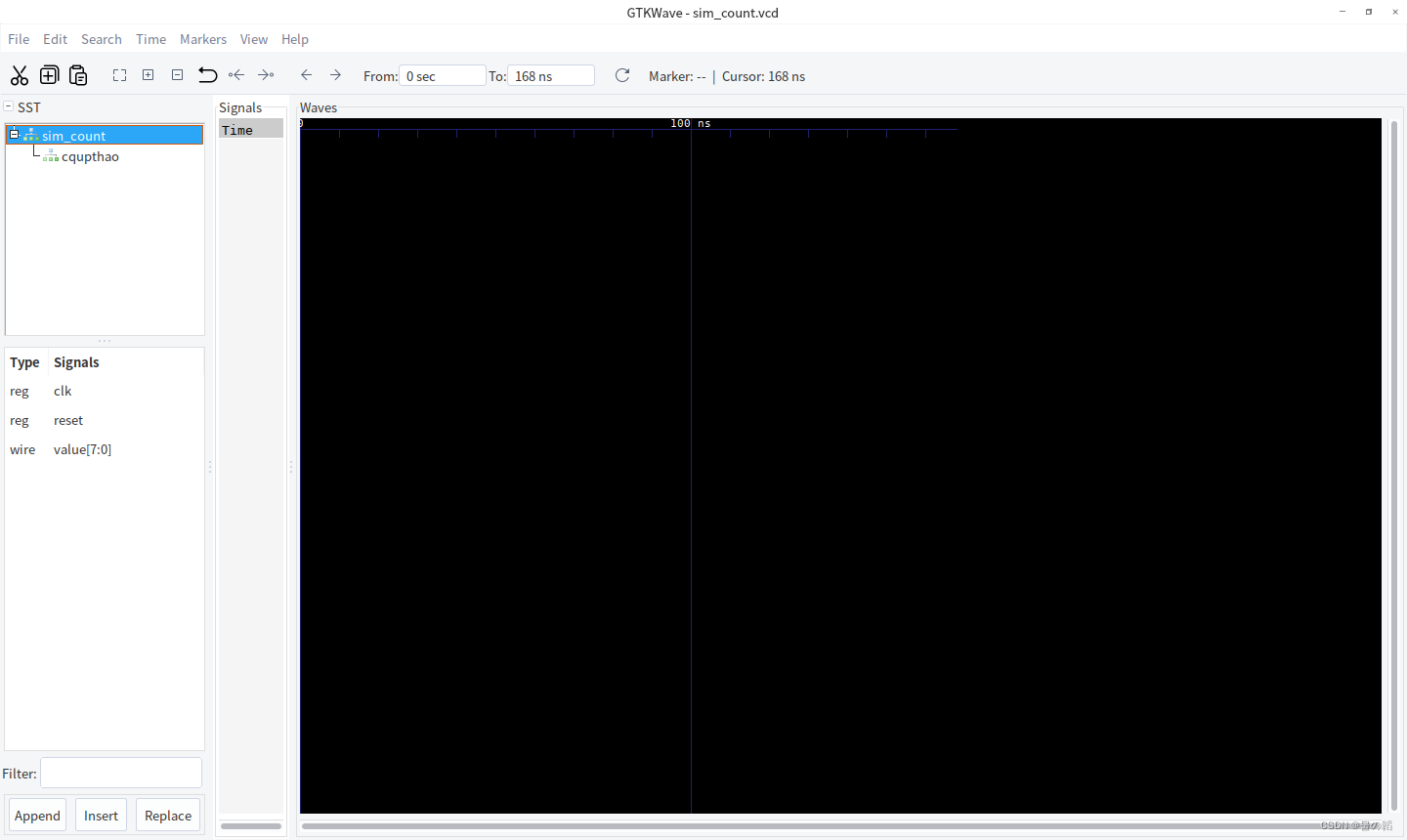

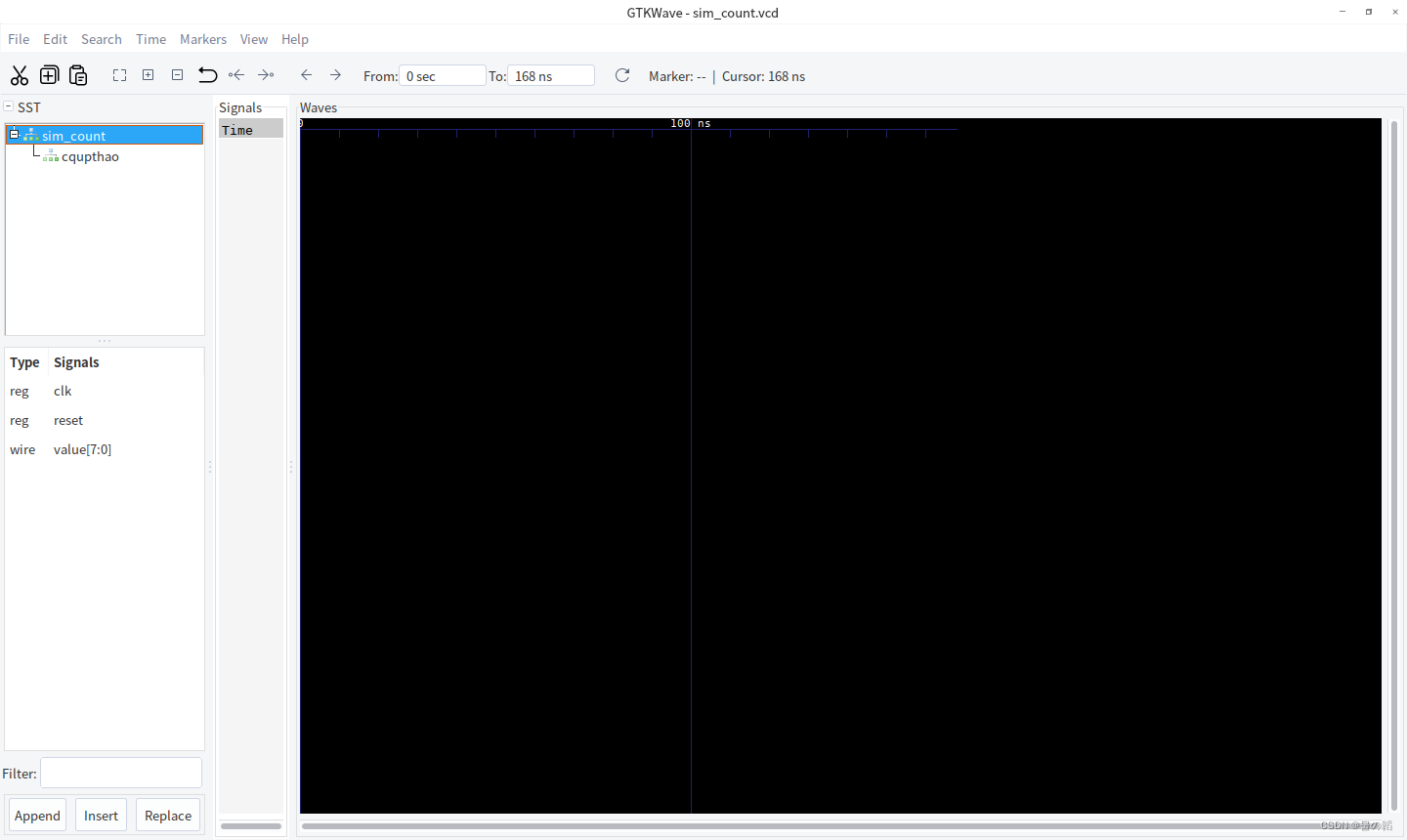

(4)gtkwave 软件运行成功后,点击下图中左上角的 cqupthao,会出现对应的信号。

(5)选中信号后,鼠标右键点击 Insert 后,就能看见如下图所示的波形!文章来源:https://uudwc.com/A/PdM8b

文章来源地址https://uudwc.com/A/PdM8b

文章来源地址https://uudwc.com/A/PdM8b

- 方式二

(1)在 Linux 终端执行以下命令。

iverilog -o simname count.v sim_count.v

注:在参数

-o name中,name 是输出的文件名,输出的文件是一个可执行文件。

(2)执行该文件后会出现 .vcd 波形文件 vcd ,提供给 gtkwave 软件使用,在终端中执行以下命令。

./simname

正确运行以上命令后,会输出如下图所示的结果。

注意:此刻,该项目的目录下有

count.v sim_count.v sim_count.vcd simname四个文件。

(3)成功转换文件之后将此文件导入 gtkwave 软件中,在终端中执行以下命令。

gtkwave sim_count.vcd

(4)gtkwave 软件运行成功后,点击下图中左上角的 cqupthao,会出现对应的信号。

(5)选中信号后,鼠标右键点击 Insert 后,就能看见如下图所示的波形!

- 参考博文:linux 运行verilog,Linux | “搭建verilog学习环境”