PDN仿真笔记7-使用Sigrity PowerSI进行PDN仿真的方法2

1. PDN结果分析及优化

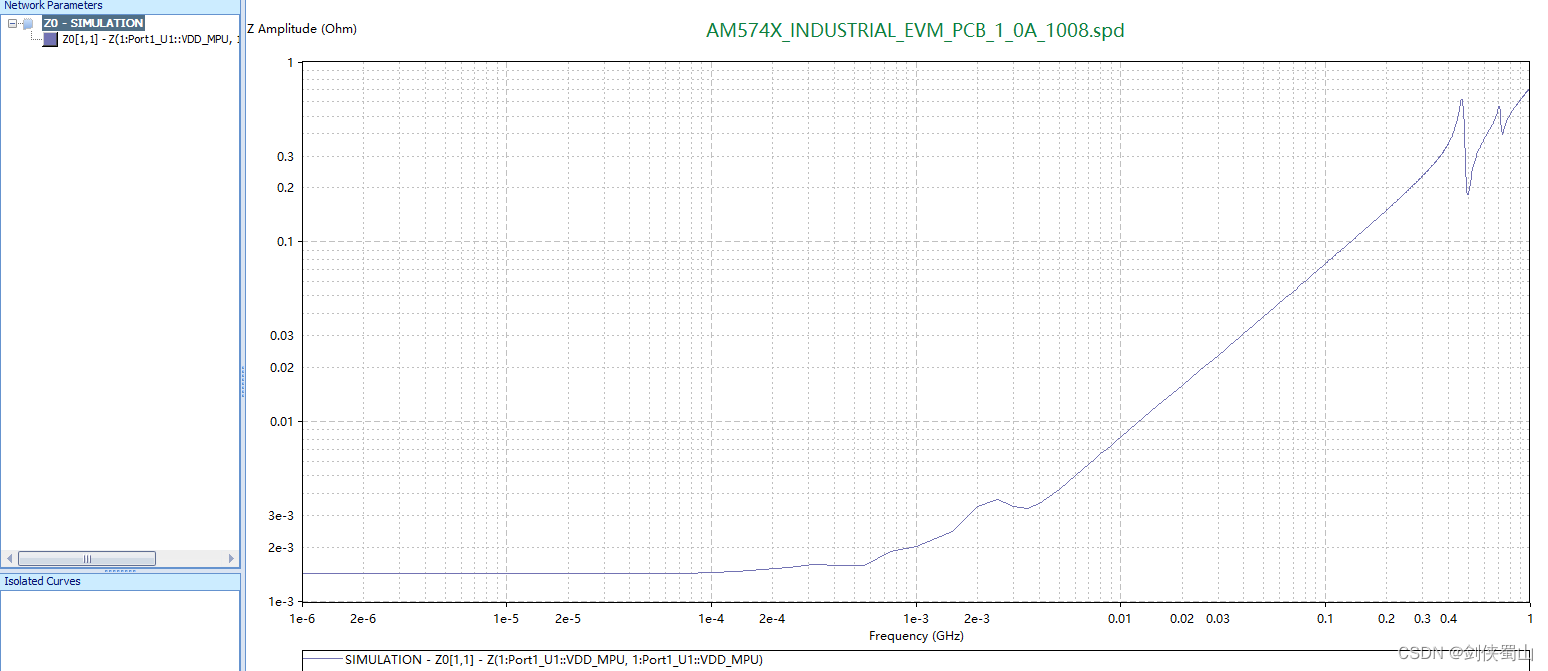

PDN仿真结果一般的波形与电容的仿真结果有点类似,低频段时阻抗偏高,随着频率的增加,受到电容的滤波效果,阻抗会逐渐降低;当滤波电容或寄生电容等电容在某个频率点达到谐振时,对应频点会出现1个阻抗的低谷;当超过谐振频率时,受寄生电感等影响,阻抗会逐渐升高。

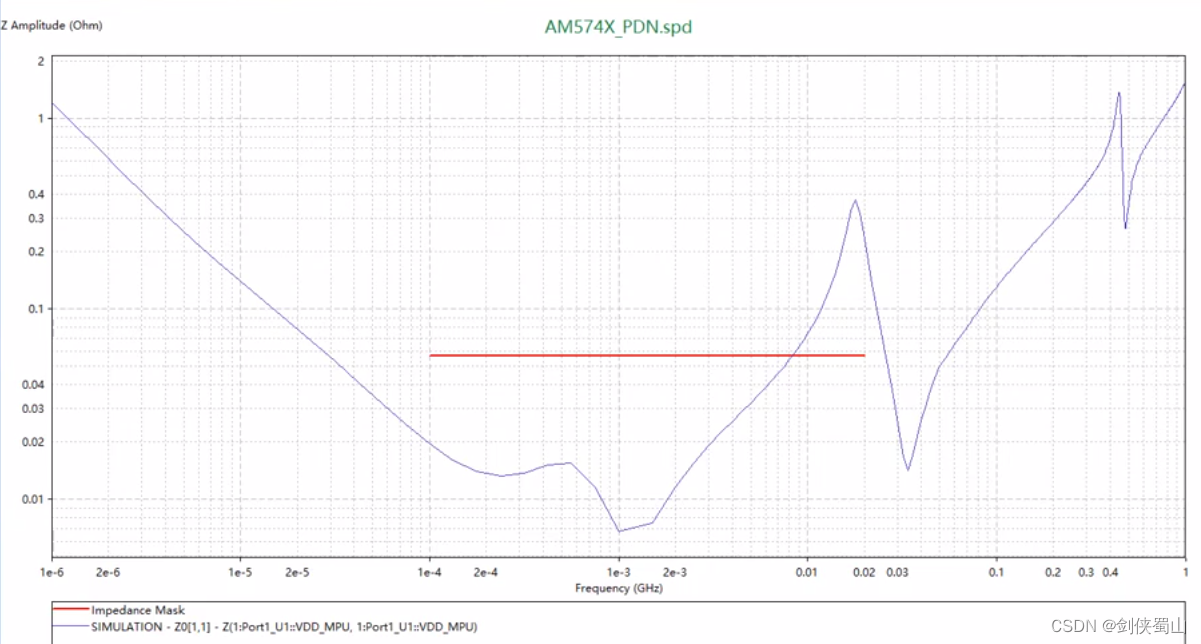

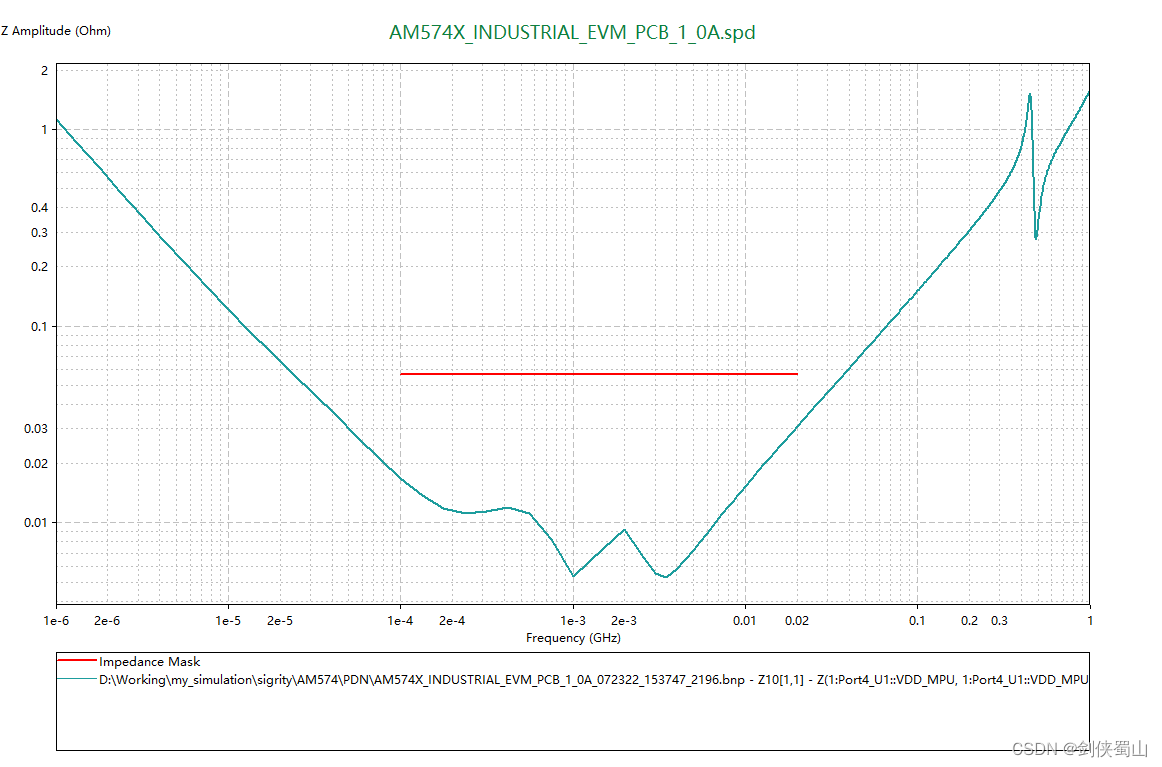

如下图的PDN仿真结果,红色为阻抗要求:

可见,在8MHz~20MHz PDN阻抗超标。

根据电容的滤波原理,参考如下链接:

https://blog.csdn.net/qq_42682826/article/details/126862030

https://blog.csdn.net/qq_42682826/article/details/126911920#t4

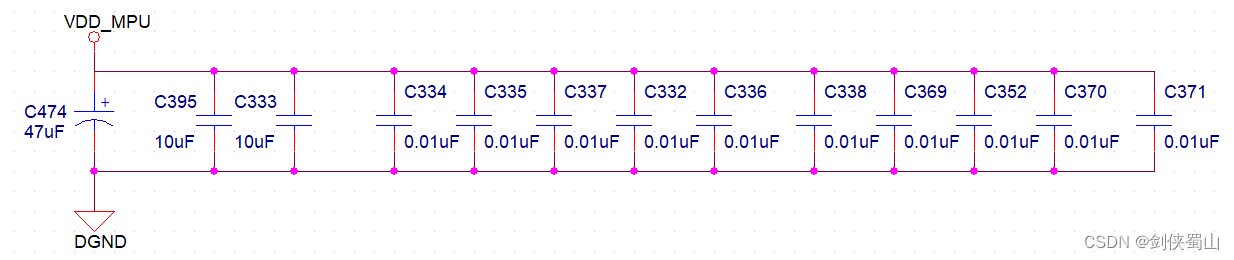

8MHz~20MHz PDN阻抗超标,主要原因可能是所选择电容的阻抗特性不满足要求,本例中所选择的滤波电容为47uF+10uF+0.01uF:

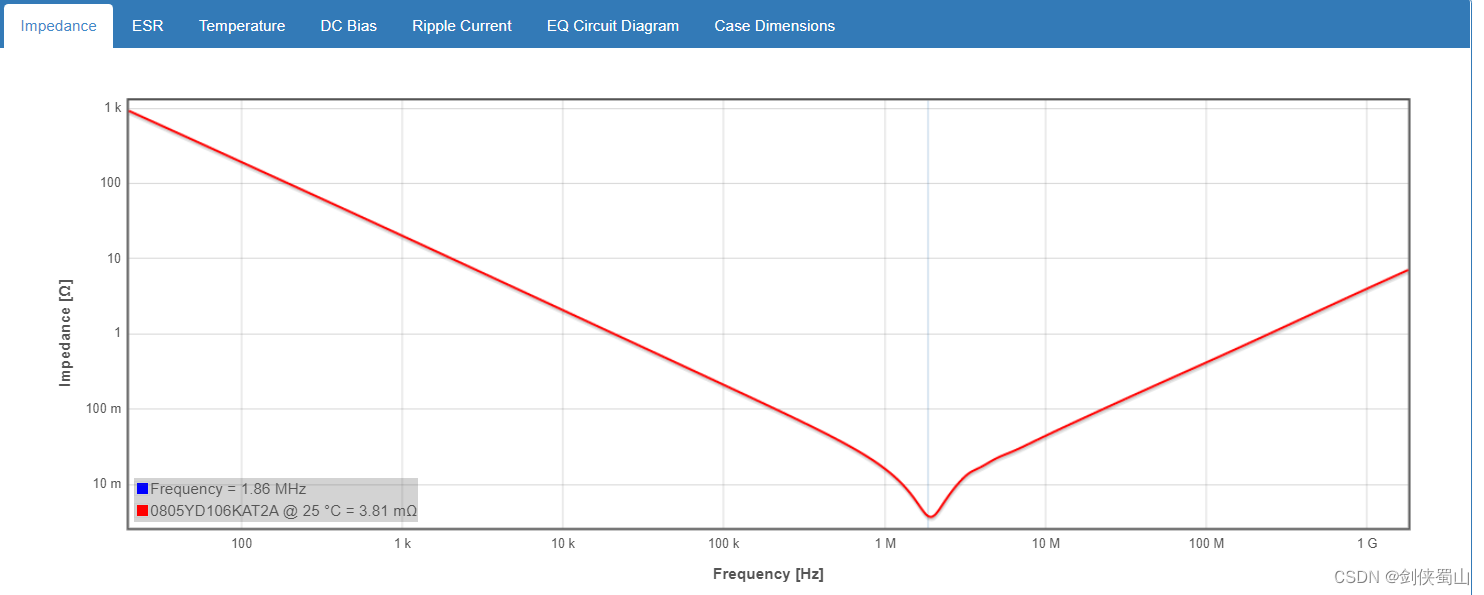

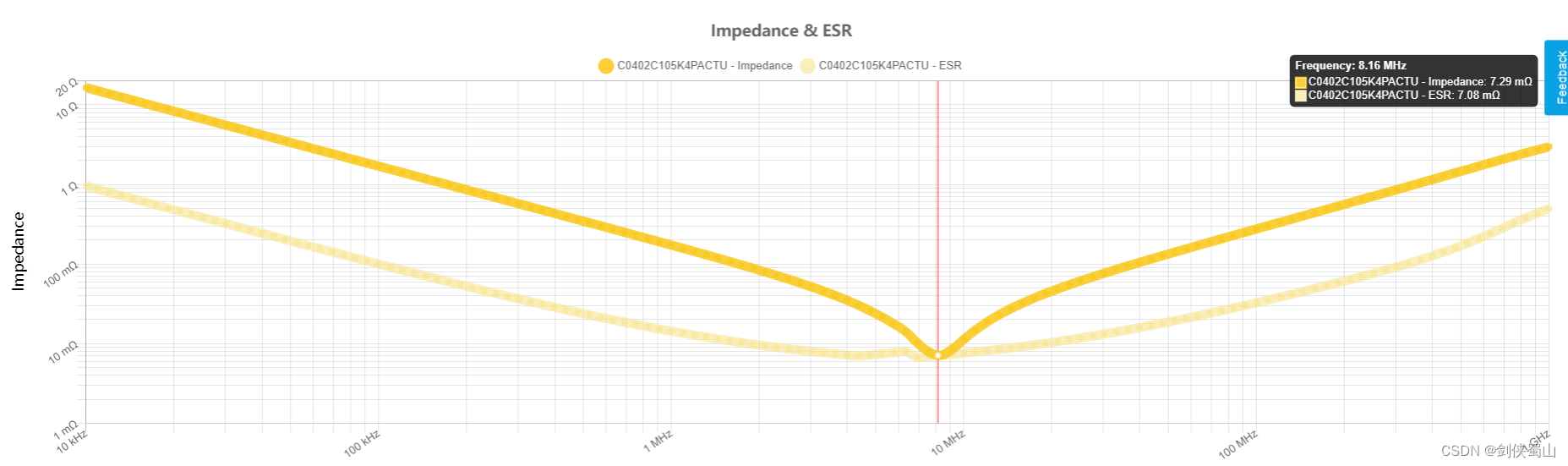

其中,10uF的阻抗曲线如下,谐振点2MHz左右:

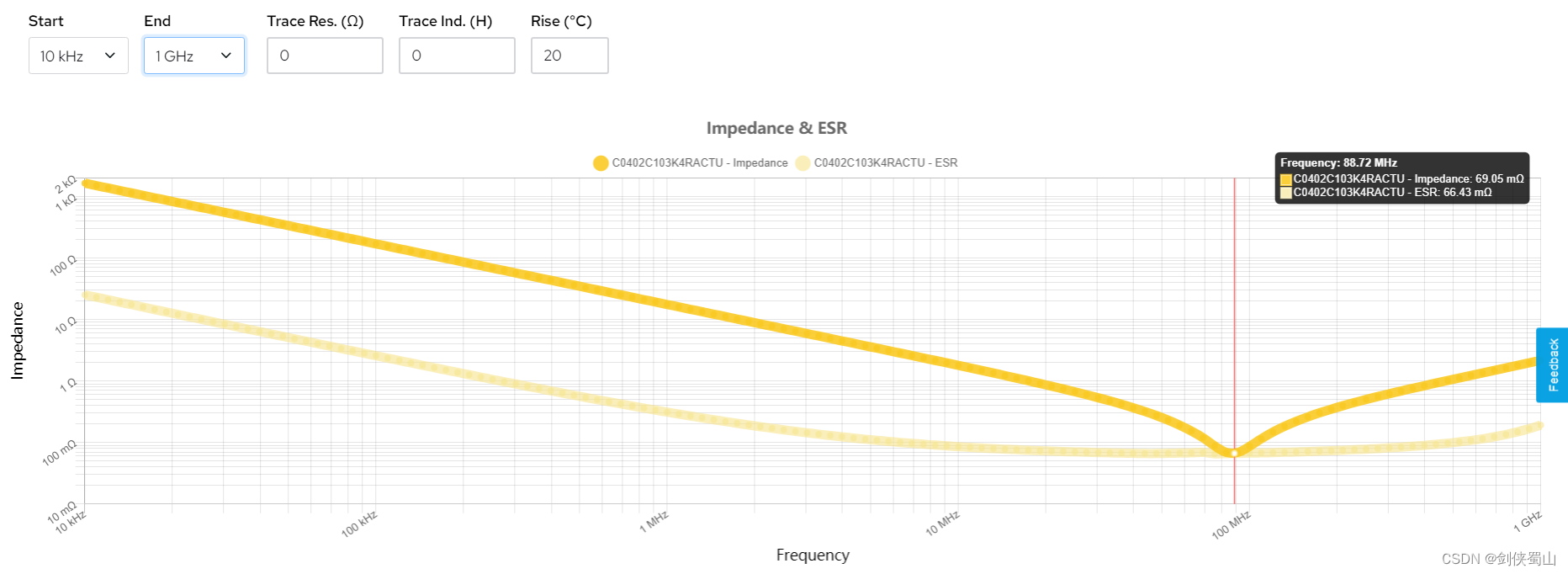

0.01uF的阻抗曲线如下,谐振点86MHz左右:

根据电容并联原理,由于10uF电容和0.01uF电容的谐振频率相差太大,并联时二者会形成并联谐振峰,从而导致并联谐振峰处阻抗超标。解决方案就是将0.01uF电容的容值增大,降低其谐振频率,或者增加处于10uF和0.01uF之间容值的电容。

1uF电容的阻抗曲线如下,谐振频率点与10uF相差不是太多。将所有0.01uF电容替换为1uF电容(多个1uF电容并联会降低总体阻抗)

电容组合修改后的仿真结果如下,可以看出,更新电容组合后,PDN仿真结果满足spec要求。

综上:

当PDN不满足设计要求时,需要根据仿真结果,优化电容组合,尽量不使用谐振频点相差太多的组合,应使用谐振频点逐步增大的方式进行电容选择。

2. 电源短路仿真与开路仿真

在进行PDN仿真时,有开路仿真和短路仿真两种方式,具体使用哪种方式,一般根据芯片厂商的要求进行。比较常见的是开路仿真,如PDN仿真笔记6所述。

PDN仿真笔记6

对于短路仿真来说,有两种方式:

(1)在DCDC端将输出与GND短接

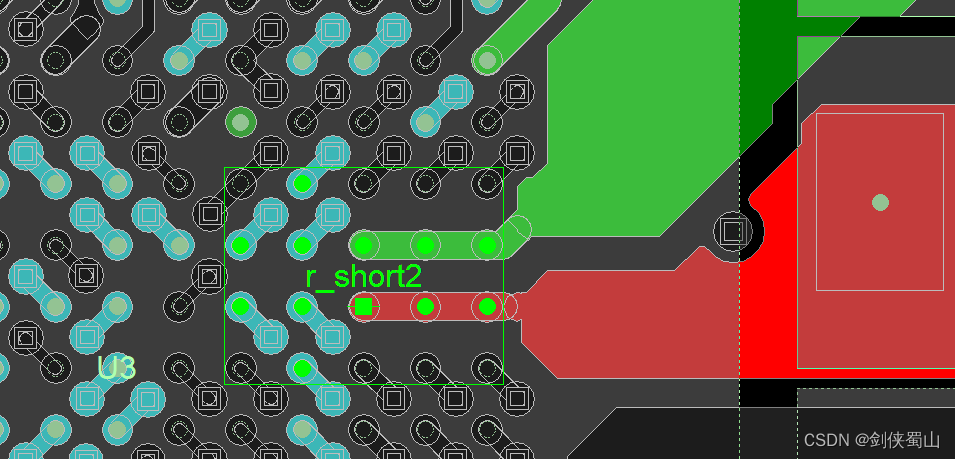

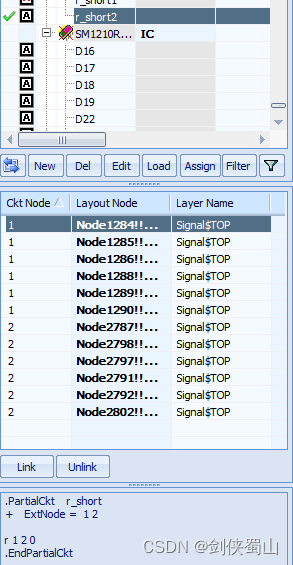

在电源的DCDC端,将电源输出的正负极之间直接用short电阻模型短接。仿真时,依然选择的是IC端的port进行仿真,注意短路电阻要将电源pin和GND pin均连接起来。

这种情况下,仿真时可以直接输出短路仿真结果,如下图所示: 文章来源:https://uudwc.com/A/PmGO

文章来源:https://uudwc.com/A/PmGO

(2)使用矩阵计算

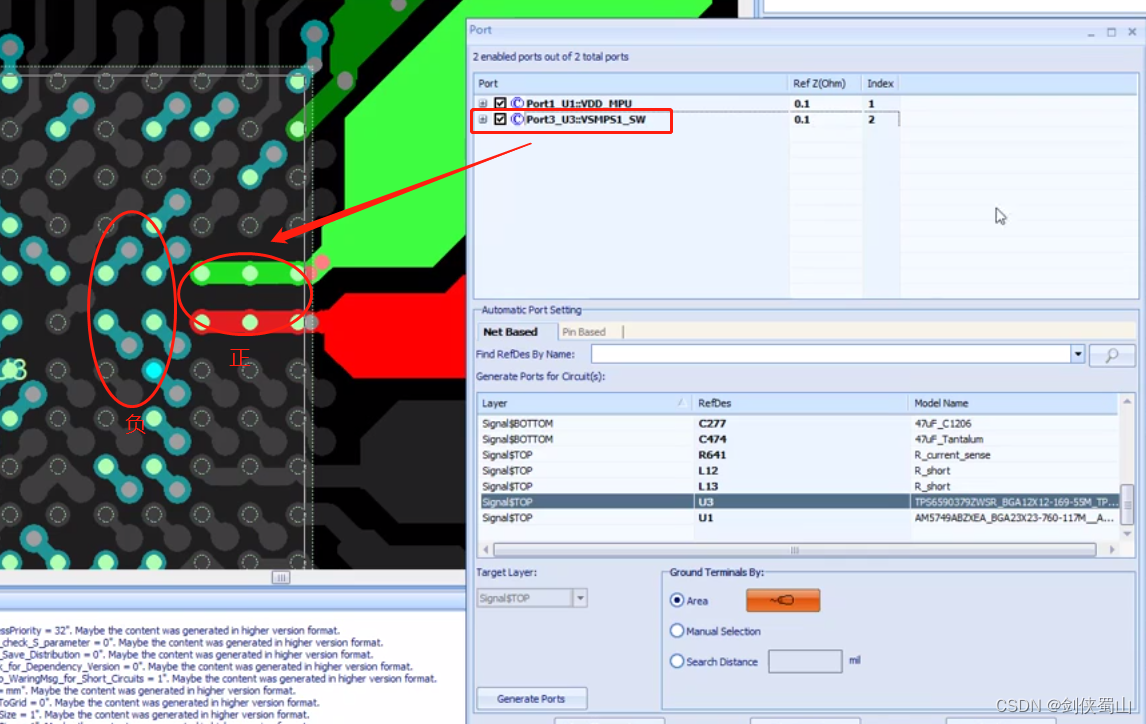

另外一种方式是,在DCDC端同样添加port,即同时仿真IC端的port和DCDC端的port。

DCDC端的port需要将所有正极及对应回流的负极都link到对应的port中,Ref Z注意修改为0.1ohm。

然后进行正常的仿真

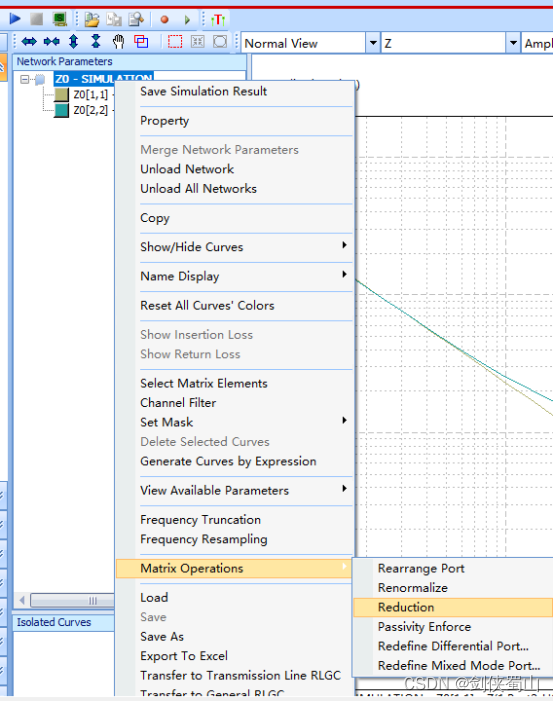

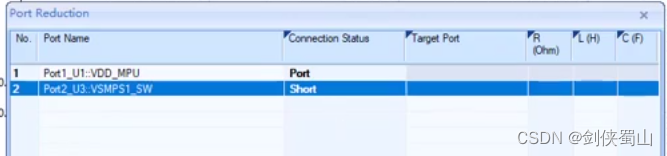

仿真结束后,在仿真结果上右键,选择“Matrix Operations”-》“Reduction”

然后将DCDC输出端“Connection Status”设置为Short,新输出的波形即为短路仿真波形

可以看出,两种方法得到的短路阻抗波形完全相同文章来源地址https://uudwc.com/A/PmGO