数字IC笔面基础之触发器

- 写在前面的话

- 关键点:

- D触发器

- 基本正边沿触发D触发器

- 异步复位D触发器

- 带清零和置一的D触发器

- T触发器

- JK触发器

- 总结

写在前面的话

触发器是数字IC最基础的知识点,区别于锁存器,触发器是只有在时钟信号触发时才能动作的存储单元,每个触发器可以存储1位二值信号。触发器有两个基本特点:

(1)具有自行保持稳定状态,包含逻辑0和逻辑1。

(2)可以根据输入信号置为1或0状态。

关键点:

笔面时常考的知识点是区分锁存器(Latch)和触发器(Flip-Flop),了解哪些代码风格可能会被综合成Latch,尽量避免。(在实际项目中有时需要故意生成Latch)

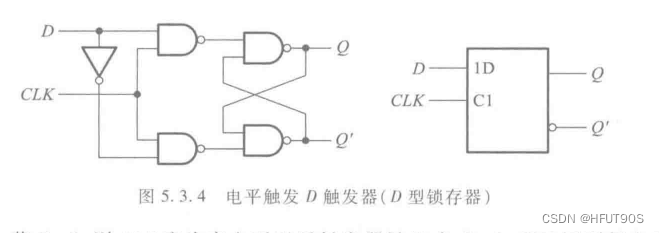

锁存器(Latch):电平触发,数据存储取决于信号的电平值。电平有效时,输出信号被锁存。

锁存器如下:

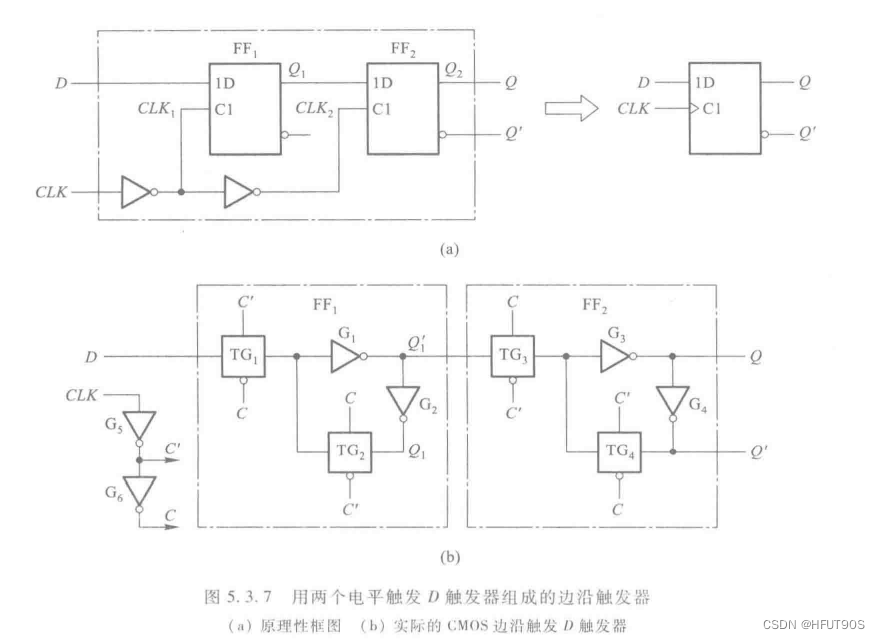

触发器(Flip-Flop):边沿触发,数据存储取决于信号的上升沿或下降沿。

触发器如下:

寄存器(Register): Verilog中用来暂时存放数据的变量。变量被声明为寄存器时,可能被综合成Latch或者Fliop-Flop。

锁存器和触发器优缺点:

锁存器优点:

(1)面积比触发器小

门电路时构建组合逻辑电路的基础,而锁存器和触发器是构成时序逻辑电路的基础。

晶体管>>门电路>>锁存器>>触发器

Latch完成同一个功能所需的门较触发器要少,在ASIC中用的比较多。

(2)速度比触发器快

用来地址锁存是很合适,不过一定要保证所有的Latch信号源的质量,锁存器在CPU设计中很常见,锁存器使得CPU的速度比外部IO部件逻辑快很多。

锁存器缺点:

(1)电平触发,非同步设计,受布线延迟影响较大,很难保证输出没有毛刺。

(2)Latch将静态时序分析变得极其复杂。

触发器优点:

(1)边沿触发,同步设计,不容易受毛刺的影响。

(2)时序分析简单

触发器缺点:

(1)面积比Latch大,消耗的门电路比latch多。

(2)过多的触发器使得数据逻辑变得复杂。

D触发器

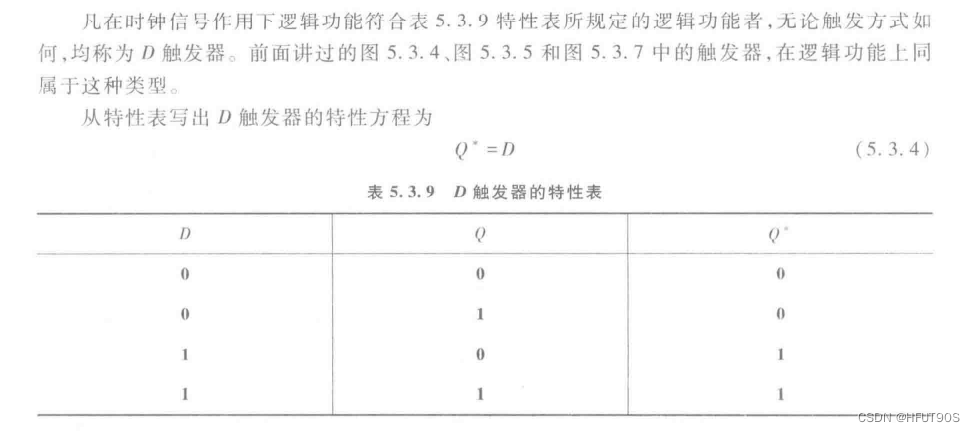

D触发器的次态取决于触发之前D端口的状态。

基本正边沿触发D触发器

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2022 All rights reserved

// -----------------------------------------------------------------------------

// Author : HFUT904 1320343336@qq.com

// File : dff.v

// Create : 2022-11-01 11:10:05

// Revise : 2022-11-01 11:10:05

// Editor : HFUT Integrated Circuit Design & Research Center

// Verdion: v1.0

// Description: 正边沿触发 DFF

// -----------------------------------------------------------------------------

module dff (

input clk , // Clock

input d , // input

output reg q // output

);

always @(posedge clk ) begin //上升沿触发

q <= d ;

end

endmodule

异步复位D触发器

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2022 All rights reserved

// -----------------------------------------------------------------------------

// Author : HFUT904 1320343336@qq.com

// File : asdff.v

// Create : 2022-11-01 11:14:23

// Revise : 2022-11-01 11:14:23

// Editor : HFUT Integrated Circuit Design & Research Center

// Verdion: v1.0

// Description: 异步复位 DFF

// -----------------------------------------------------------------------------

module asdff (

input clk , // Clock

input rst_n , // Asynchronous reset active low

input d , // input

output reg q //output

);

always @(posedge clk or negedge rst_n) begin

if(~rst_n) begin

q <= 1'b0 ;

end

else begin

q <= d ;

end

end

endmodule

带清零和置一的D触发器

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2022 All rights reserved

// -----------------------------------------------------------------------------

// Author :HFUT904 1320343336@qq.com

// File : csdff.v

// Create : 2022-11-01 15:23:49

// Revise : 2022-11-01 15:23:49

// Editor : HFUT Integrated Circuit Design & Research Center

// Verdion: v1.0

// Description: 带清零和置位 DFF

// -----------------------------------------------------------------------------

module csdff (

input clk , // Clock

input set , // set

input rst_n , // Asynchronous reset active low

input d , //input

output reg q //output

);

always @(posedge clk , negedge rst_n , posedge set) begin

if(~rst_n) begin

q <= 1'b0 ;

end

else if(set) begin

q <= 1'b1 ;

end

else begin

q <= d ;

end

end

endmodule

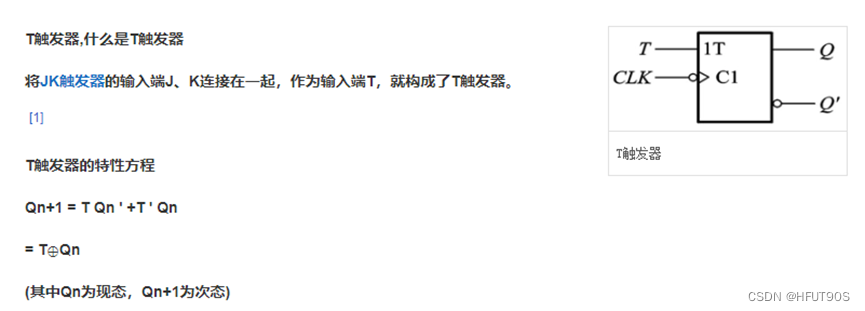

T触发器

T触发器是在数字电路中,凡在CP时钟脉冲控制下,根据输入信号T取值的不同,具有保持和翻转功能的触发器,即当T=0时能保持状态不变,当T=1时一定翻转的电路。

// Copyright (c) 2014-2022 All rights reserved

// -----------------------------------------------------------------------------

// Author : HFUT904 1320343336@qq.com

// File : tff.v

// Create : 2022-11-01 15:31:04

// Revise : 2022-11-01 15:31:04

// Editor : HFUT Integrated Circuit Design & Research Center

// Verdion: v1.0

// Description:TFF

// -----------------------------------------------------------------------------

module tff (

input clk ,

input rst_n ,

input T ,

output reg Q

);

//特征方程写法

always @(posedge clk or negedge rst_n) begin

if(~rst_n) begin

Q <= 0;

end

else begin

Q <= (T&~Q)|(~T&Q) ;

end

end

//查找表写法

/*

always@(posedge clk) begin

if(T==1'b1)

Q <= ~Q ;

else

Q <= Q ;

end

*/

endmodule

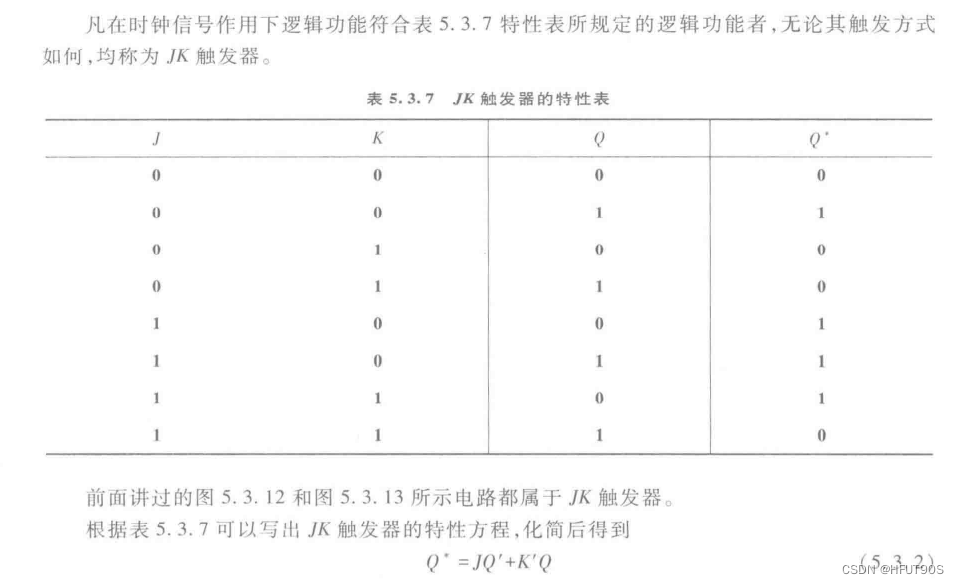

JK触发器

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能。在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。 文章来源:https://uudwc.com/A/Xkx4

文章来源:https://uudwc.com/A/Xkx4

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2022 All rights reserved

// -----------------------------------------------------------------------------

// Author : HFUT904 1320343336@qq.com

// File : jkff.v

// Create : 2022-11-01 15:33:16

// Revise : 2022-11-01 15:33:16

// Editor : HFUT Integrated Circuit Design & Research Center

// Verdion:

// Description:

// -----------------------------------------------------------------------------

module jkff (

input clk ,

input rst_n ,

input J ,

input K ,

output reg Q

);

//状态方程写法

always @(posedge clk or negedge rst_n) begin

if(~rst_n) begin

Q <= 1'b0;

end

else begin

Q <= (J&~Q)|(~K&Q) ;

end

end

//查找表写法

/*

always@(posedge clk ) begin

case({J,K})

2'b00: Q <= Q ;

2'b01: Q <= 1'b0 ;

2'b10: Q <= 1'b1 ;

2'b11: Q <= ~Q ;

endcase

end

*/

endmodule

总结

触发器作为数字IC最基础的内容,常常会考手撕代码、门级电路组成、与锁存器的优缺点、代码风格避免生成latch等内容。在跨时钟域中也会用两级DFF避免亚稳态的产生,我在笔面中遇见最多的是DFF和TFF,会结合建立时间、保持时间、跨时钟域、代码风格等一起考。建议各位同学注意触发器的底层电路,切实体会触发器和锁存器的区别。文章来源地址https://uudwc.com/A/Xkx4