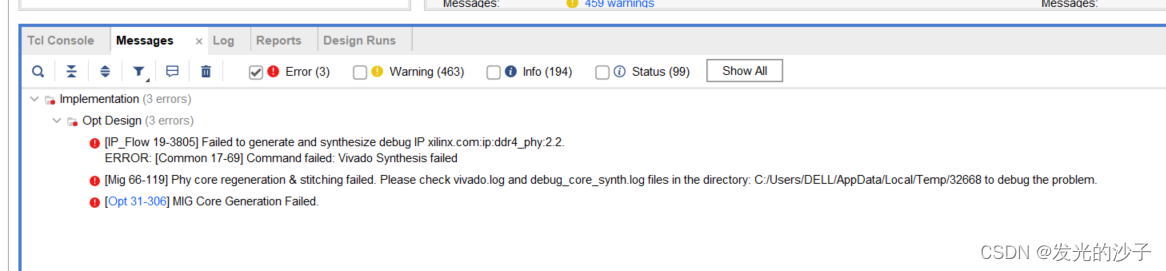

1、在Vivado 2019.1版本中使用DDR4的IP核会遇到如下图所示的错误,即便过了implementation生成了bit,DDR4也无法正常启动。

2、解决办法,上xilinx社区搜一下就知道了

AMD Customer Community![]() https://support.xilinx.com/s/article/69035?language=en_US这是关于DDR4的所已知问题的解决方案 AMD Customer Community

https://support.xilinx.com/s/article/69035?language=en_US这是关于DDR4的所已知问题的解决方案 AMD Customer Community![]() https://support.xilinx.com/s/article/73052?language=en_US

https://support.xilinx.com/s/article/73052?language=en_US

这是关于“[Mig 66-119] Phy core regeneration & stitching failed. Please check vivado.log and debug_core_synth.log files in the directory: C:/Users/DELL/AppData/Local/Temp/32668 to debug the problem.

”问题的解决方案。

[66-119]错误在2019.2版本可安装两个补丁包解决。在2019.2.1版本以后可以完美解决。

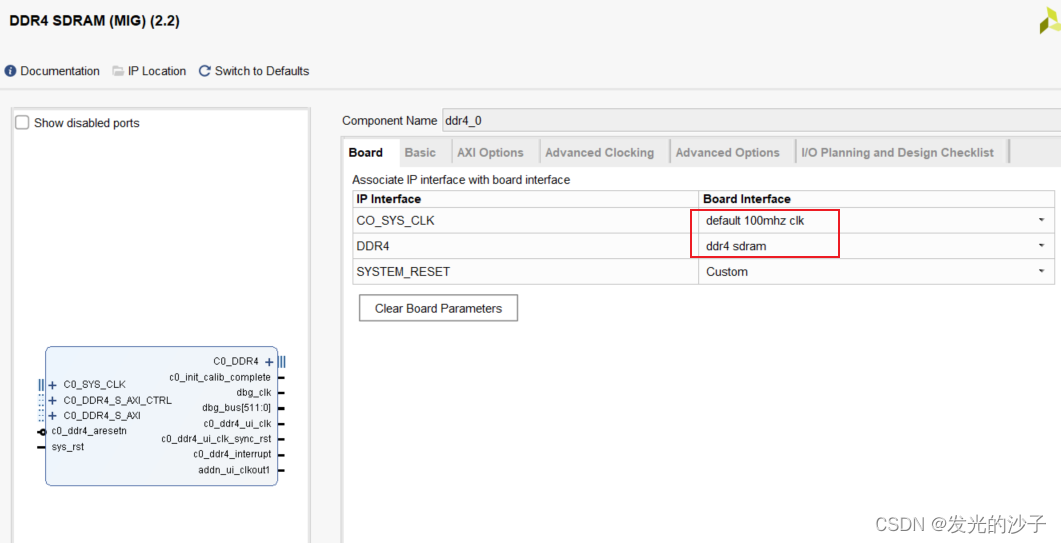

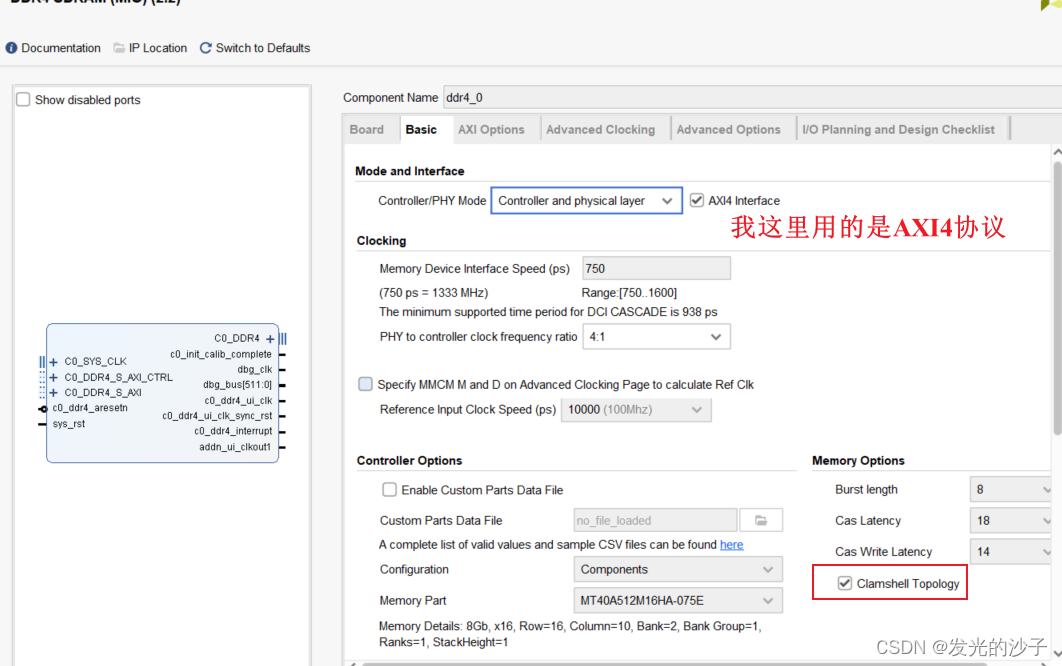

3、需要注意的是,VCU128的DDR4配置,应当按如下方法配置,不然无法使用。

文章来源:https://uudwc.com/A/ZG8qx

文章来源:https://uudwc.com/A/ZG8qx

上面这个框貌似必须勾选,对应c0_ddr4_cs_n端口,可以防止发生致命错误。文章来源地址https://uudwc.com/A/ZG8qx

上面这个框貌似必须勾选,对应c0_ddr4_cs_n端口,可以防止发生致命错误。文章来源地址https://uudwc.com/A/ZG8qx