-

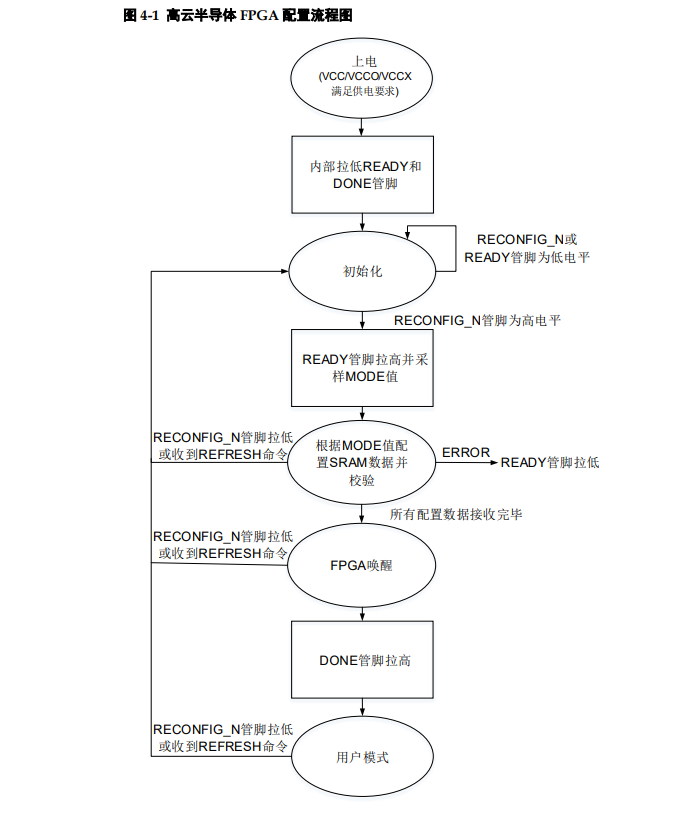

高云半导体 FPGA 配置流程图

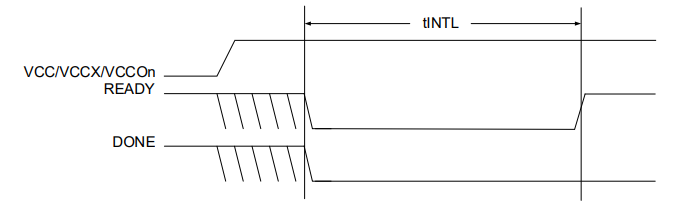

4.1 上电时序

电源上电的过程中,FPGA 内部的上电复位(POR)电路开始工作。POR

电路确保外部 I/O 管脚处于高阻状态并监控 VCC/VCCX/VCCOn 电源轨。

当 VCC/VCCX/VCCOn 满足最低复位电平时(不同器件的复位电平不同,不

同器件监控的电源轨不同),POR 电路释放内部复位信号,FPGA 开始初始

化流程。当 READY 和 DONE 信号拉低后,器件进入初始化状态,如图 4-2

所示。

图 4-2 POR 上电时序图

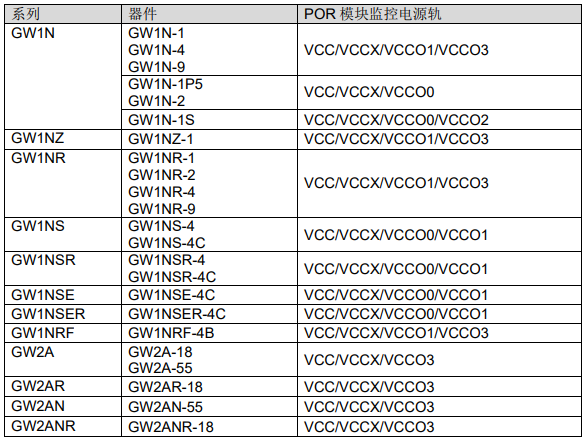

表 4-1 列出了不同器件 POR 模块监控电源轨的详情。

表 4-1 不同器件 POR 模块监控电源轨

4.2 初始化

在上电复位电路拉低 READY 和 DONE 管脚后,高云半导体 FPGA 立

即进入存储器初始化状态。初始化状态的目的是清除 FPGA 内部的配置

SRAM 存储器。

FPGA 满足以下所有条件后跳出初始化状态:

l 初始化状态超过 tINITL

l RECONFIG_N 管脚为高

l READY 管脚不被外部驱动强制拉低

在初始化阶段 READY 管脚提供两种功能:

1. 指示 FPGA 正在清除内部的配置 SRAM 区域;

2. 作为输入,当被外部强制拉低时可以阻止 FPGA 跳出初始化状态。

4.3 配置

识别到 READY 管脚的上升沿后,FPGA 进入配置状态。根据 MODE

管脚状态,可以通过多种模式配置 FPGA 内部的配置 SRAM。在 FPGA 接

收配置数据的期间,可以通过 READY 管脚判别内部状态。READY 管脚高

电平指示配置过程正常,READY 管脚低电平指示 FPGA 配置出错,不能正

常工作。

4.4 唤醒

当正确接收到所有配置数据后,FPGA 进入唤醒状态并置起内部的

DONE 状态位。在唤醒状态下,FPGA 会依次进行如下操作:

1. 使能全局输出信号(GOE),FPGA 的 I/O 退出高阻状态,完成 I/O 编程

实现预设的功能。通过置位全局置位/复位信号(GSR),可以防止输入信

号影响 FPGA 内部的 Flip-Flop 状态。

2. 释放全局置位/复位信号(GSR)和全局写入禁止信号(GWDISn)。使能

全局写入禁止信号可以防止 FPGA 误改写内部 RAM 的初始化数据。

3. 使能外部 DONE 管脚。使能状态下 DONE 管脚是一个双向开漏 I/O。

可以通过外部强制拉低 DONE 管脚的方式让 FPGA 保持在唤醒状态。

一旦 DONE 管脚拉高,FPGA 将完成唤醒状态,进入用户模式。

4.5 用户模式

进入用户模式后,FPGA 将立刻执行您设计的逻辑运算。FPGA 将保持

在用户模式下直到触发以下三种事件:

l 外部拉低 RECONFIG_N 管脚

l 通过配置端口接收到 REFRESH 指令

l 电源有下上电动作

一旦出现以上三种操作,FPGA 将重新进入配置流程。

5.1 配置管脚列表及复用选项

文章来源地址https://uudwc.com/A/oLRpE

5.1.1 配置管脚列表

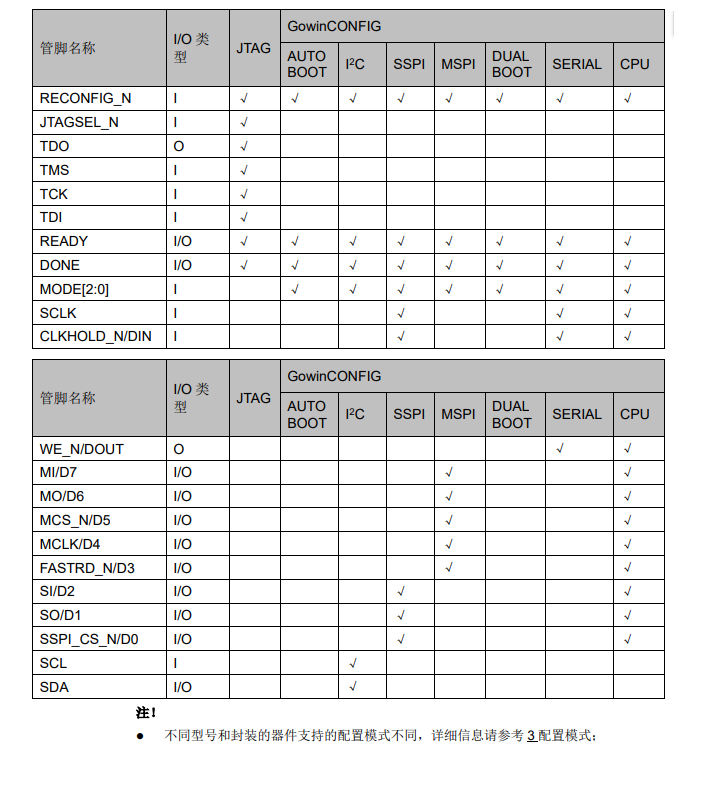

高云半导体 FPGA 产品所有与配置相关的管脚如表 5-1 所示,表中也

标注了每种配置模式使用到的管脚及芯片封装过程中的管脚共用情况。

表 5-1 配置管脚列表

文章来源:https://uudwc.com/A/oLRpE

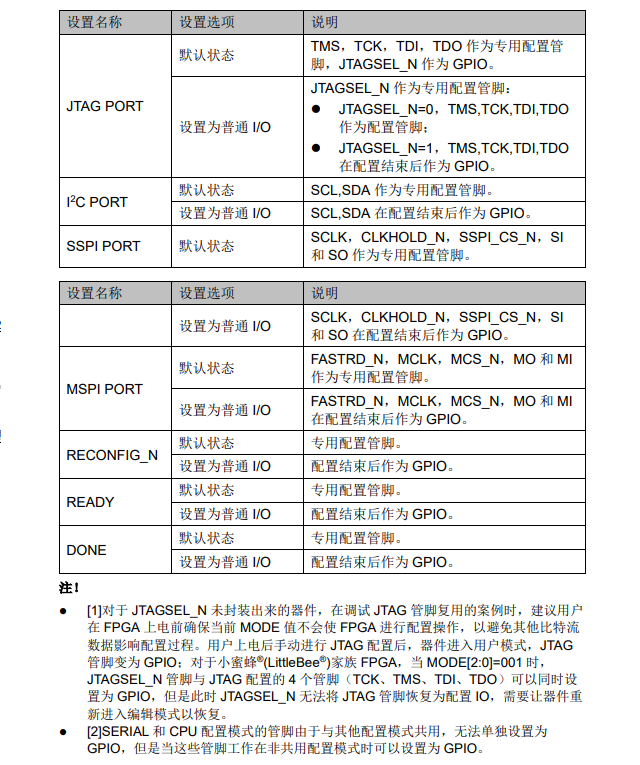

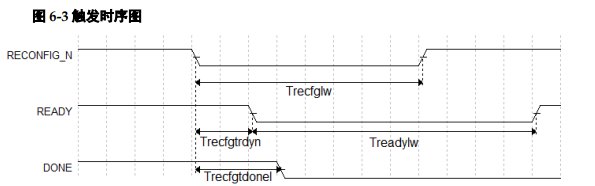

5.1.2 配置管脚复用

为最大化地提高 I/O 的利用率,高云半导体的 FPGA 产品支持将配置管脚设置为普通 I/O 使用。所有系列的 FPGA 上电后未进行任何配置操作之前,与配置相关的管脚均默认作为配置管脚使用。配置成功后,器件进入用户模式,按照用户选择的复用选项重新分配管脚的功能。

注!

用户设置管脚复用选项时,需确保管脚的外部初始连接状态不影响器件的配置过程。对于影响配置的连接,需要先进行隔离处理,等待 FPGA 进入用户模式后再进行修改。

配置管脚复用选项如表 5-2 所示。

表 5-2 配置管脚复用选项

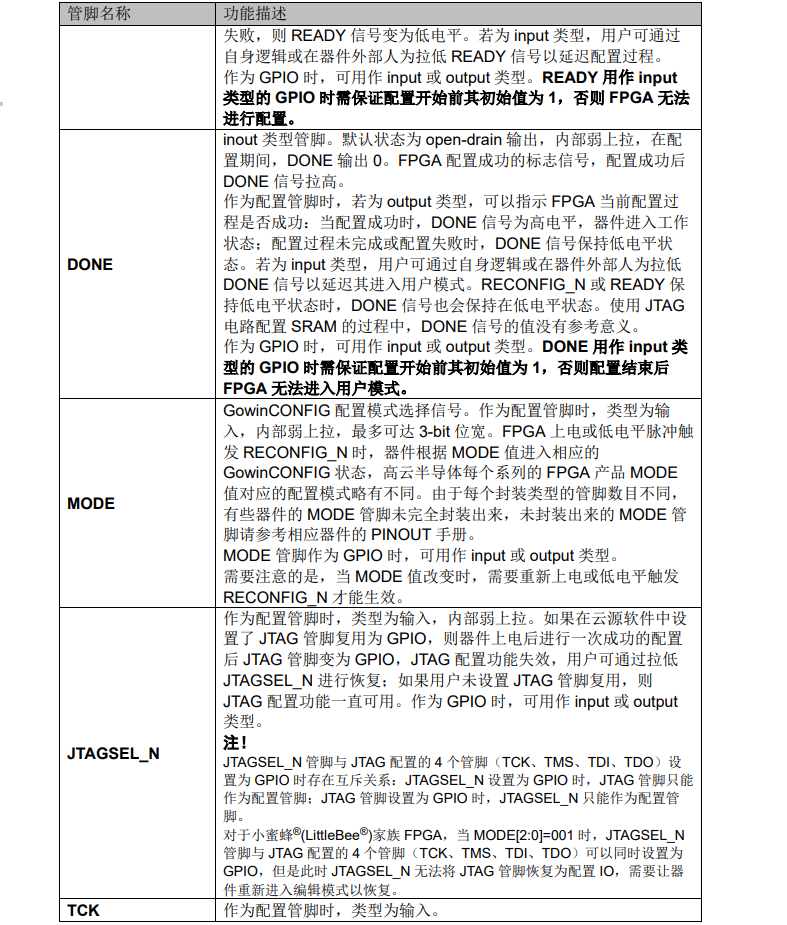

5.2 配置管脚功能及应用

RECONFIG_N、READY 和 DONE 管脚是每种模式都会用到的管脚。其他配置管脚可根据具体应用设置为配置专用管脚或普通管脚。

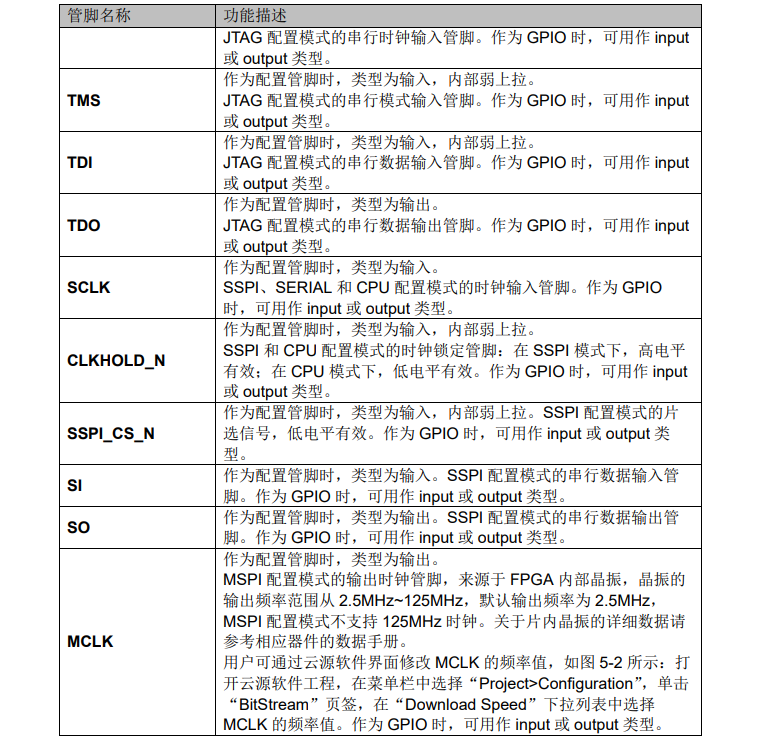

表 5-3 管脚功能

6配置模式介绍

高云半导体 FPGA 产品包含基于 SRAM 工艺的晨熙®(Arora)家族的高性能器件和嵌入 Flash 的小蜜蜂®(LittleBee®)家族的小容量非易失器件。基于 SRAM 工艺的器件掉电后器件内部的配置数据丢失,每次上电后需重新配置;嵌入 Flash 的非易失器件掉电后数据仍然存储在芯片内部,重新上电时可以通过自启动配置或双启动配置的方式由器件自动进行重新配置。

高云半导体 FPGA 产品封装类型丰富,每一种封装的器件支持的配置模式与封装出来的配置管脚数目有关:所有器件均支持通用的 JTAG 配置;只有非易失器件支持自启动或双启动配置;每种配置模式的 MODE 值各不相同。

6.1 配置须知

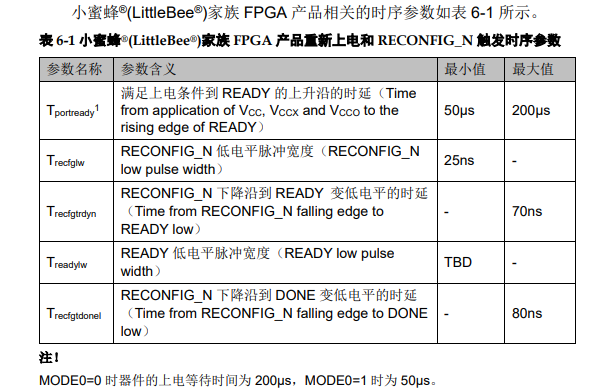

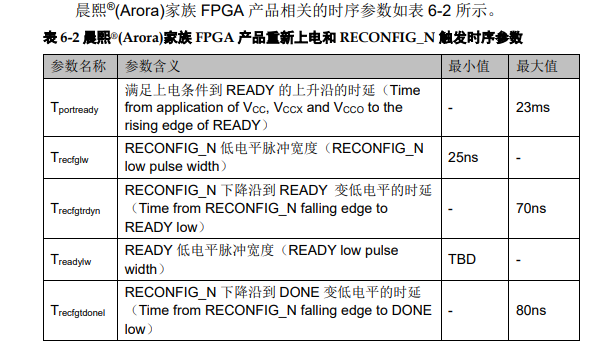

高云半导体 FPGA 产品目前分为小蜜蜂®(LittleBee®)家族和晨熙

®(Arora)家族。两大家族器件名称中是否包含 R 不影响配置特性,主要区别是带 R 的 FPGA 内部集成了 SDRAM/PSRAM。器件名称中包含 S 的

FPGA 除了双启动配置特性与 GW1N 系列略有差异之外,其他特性完全相同。

上电及配置流程

当 FPGA 的 VCC、VCCO、VCCX 供电电压满足最小供电幅值时,

FPGA 进入启动流程:电压稳定且 RECONFIG_N 未被外部电路拉低>FPGA 内部电路拉低 READY 和 DONE 管脚>FPGA 初始化>READY 拉高并采样 MODE 值>根据配置模式读取配置数据并校验>FPGA 唤醒>DONE 拉高>进入用户模式。 FPGA 启动过程中需要保持供电稳定,FPGA 上电稳定后的 1ms 之内以及 FPGA 初始化过程中 RECONFIG_N 管脚不允许出现低电平,用户可选择将 RECONFIG_N 管脚悬空或外部上拉。FPGA 唤醒前所有普通 I/O 输出高阻态。

高云半导体 FPGA 产品按照配置数据的存储和指令的作用位置分为对

SRAM 的操作、对内置 Flash 的操作和对外部 Flash 的操作,其中,对内置

Flash 的操作只有小蜜蜂®(LittleBee®)家族产品支持,对 SRAM 和外部

Flash 的操作所有产品均可支持。

SRAM 操作

对 SRAM 的操作包括读取器件 ID CODE 和 USER CODE,读取器件状态寄存器信息以及 SRAM 配置。器件 ID 验证是配置操作的前提,只有

ID 验证成功的器件才能进行配置;USER CODE 是为方便用户对 ID CODE

相同的多个器件加以区分进行的编号标识;器件的状态寄存器记录着 FPGA

配置前后的状态信息,用户可据此分析器件状态,状态寄存器的含义请参考表 6-12 Status Register 与配置加载相关的条目。SRAM 配置操作时需要注意,只有未设置安全位的比特流数据支持验证功能。设置了安全位的数据任何用户无法进行回读验证。

内置/外部 Flash 操作

对内置 Flash 的操作包括擦除、编程和验证操作。只能通过 JTAG 接口操作内置 Flash,时钟速率不小于 1MHz,时钟速率详见表 6-9 JTAG 的

TCK 频率要求。

注!

使用内置 Flash 配置 SRAM 的操作(自启动配置和双启动配置)和内置 Flash 的编程操作过程中 FPGA 需要保持上电状态并且不能低电平触发 RECONFIG_N,否则可能会对内置

Flash 造成不可修复的破坏。

小蜜蜂®(LittleBee®)家族的器件(GW1N-4A 除外)支持 JTAG[1]背景升级的特性,即器件支持在不影响现有工作状态的情况下通过 JTAG 接口编程内嵌 Flash 或外部 Flash 的操作,编程过程中器件可以按照原有的配置正常工作,编程完成后,低电平触发 RECONFIG_N 即可完成在线升级。此特性适合应用于在线时间长但又需要不定期升级的场所。

注! [1] GW1N-1P5 和 GW1N-2 可通过使用 goConfig I2C IP 来支持 I2C 背景升级。推荐使用

JTAG 接口进行背景升级。

配置管脚复用

用户在使用不同配置模式时,需要根据配置管脚的作用,确保 FPGA

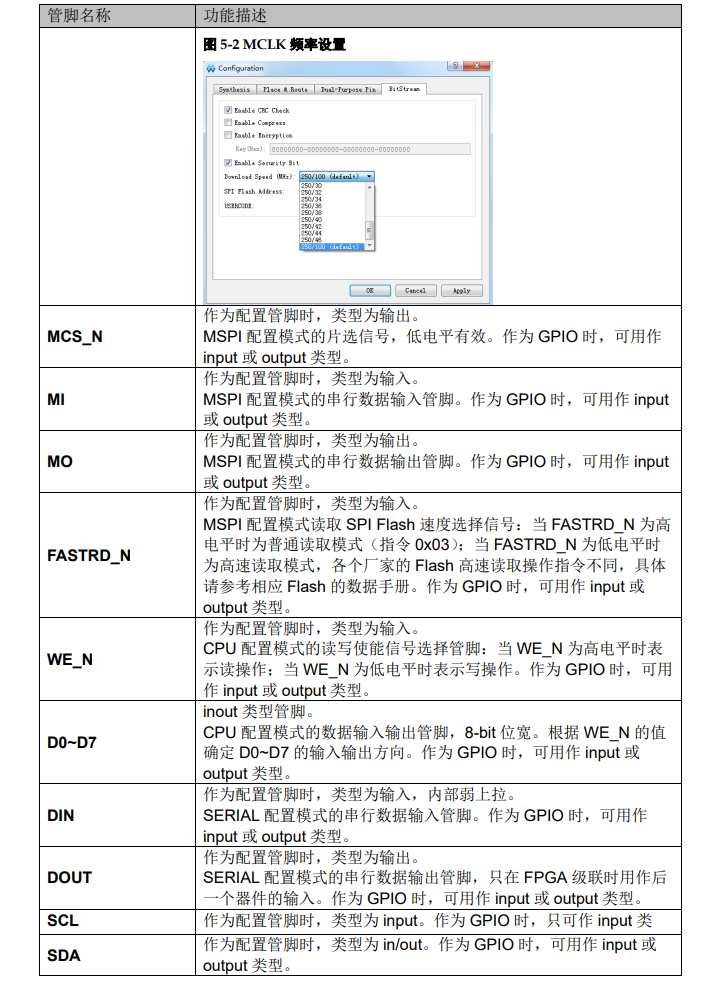

工作在已选择的配置模式下。用户端管脚数目不足时,可以通过其他连接方式灵活处理这些管脚,只保留数据传输相关的管脚即可。MODE[2:0]用来选择 GowinCONFIG 的编程配置模式,用户不需要改变模式时可以使用上拉或下拉的方式将其固定在特定的模式,上拉电阻推荐 4.7K,下拉电阻推荐

1K。

注! RECONFIG_N、READY 和 DONE 管脚与每种配置模式相关,无论用户是否将它们设置为

GPIO,都需要保证在配置操作完成前它们的初始值或管脚连接状态满足编程配置条件。

固定管脚推荐接法

用户进行电路原理图设计时,推荐接法如图 6-1 所示。

注!

用户需要改变 MODE 值时可增加拨码开关;部分器件 MODE 管脚未完全封装出来,未封装的 MODE 管脚已内部接地(GW1N(R)-2 和 GW1N-1P5 器件除外,需参考相应的 pinout 手册);

JTAG 配置过程中 READY 和 DONE 信号的值没有参考意义;

RECONFIG_N、READY 和 DONE 未封装出来的管脚已内部处理,不影响配置功能。

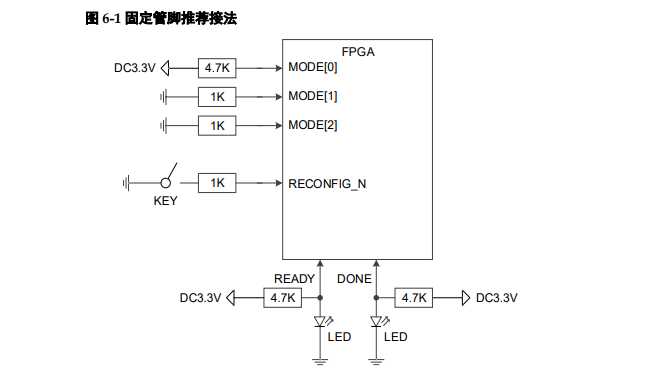

重新上电及低电平脉冲触发 RECONFIG_N 时序图

重新上电和低电平脉冲触发 RECONFIG_N 的时序图如图 6-2 和图 6-3

所示。

图 6-2 重新上电时序图

6.2 JTAG 配置

高云半导体 FPGA 产品的 JTAG 配置模式符合 IEEE1532 标准和

IEEE1149.1 边界扫描标准。 JTAG 配置模式是将比特流数据写入到高云半导体 FPGA 产品的

SRAM 中,掉电后配置数据丢失。高云半导体所有封装的 FPGA 产品均支持 JTAG 配置模式。

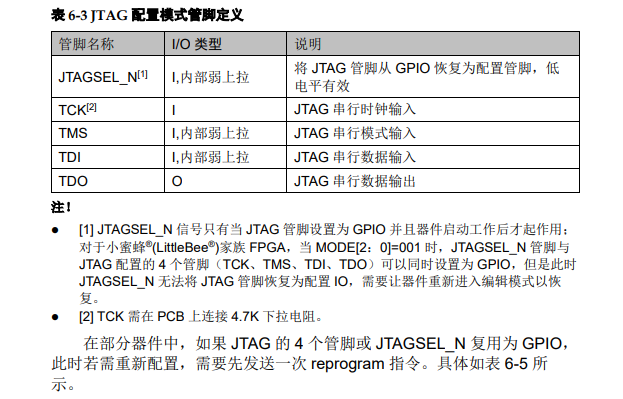

6.2.1 JTAG 配置模式管脚

JTAG 配置模式的相关管脚如表 6-3 所示。

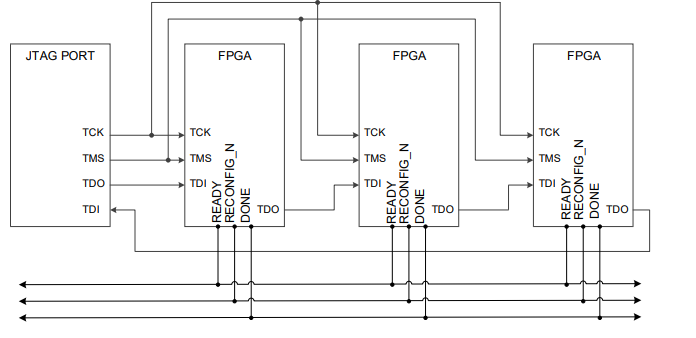

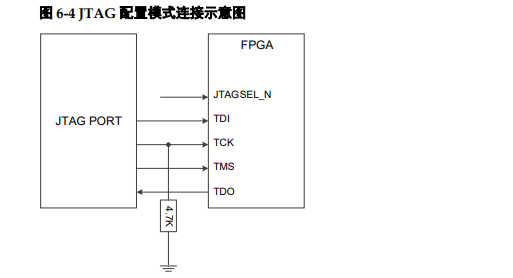

6.2.2 JTAG 配置模式连接示意图

JTAG 配置模式器件连接关系如图 6-4 所示。

注!

对于 JTAGSEL_N 未封装出来的器件,用户在调试 JTAG 管脚复用的案例时,建议上电前将 MODE 值设置为非自动配置的模式(即非自启动、双启动和 MSPI)避免其他比特流数据影响配置过程,用户上电后手动进行 JTAG 配置后,器件进入用户模式,

JTAG 管脚变为 GPIO;

JTAG 配置模式时钟频率不能高于 40MHz。

除了进行常规的 JTAG 配置 SRAM 操作外,高云半导体非易失 FPGA

器件(小蜜蜂®(LittleBee®)家族)的内置 Flash 和其他所有系列的 FPGA 产品的外部 SPI Flash 的编程操作也可通过 JTAG 管脚进行。非易失器件内置

Flash 的编程操作连线方式与 JTAG 配置模式相同,外部 SPI Flash 的编程操作请参考图 6-51 及 9 边界扫描操作。

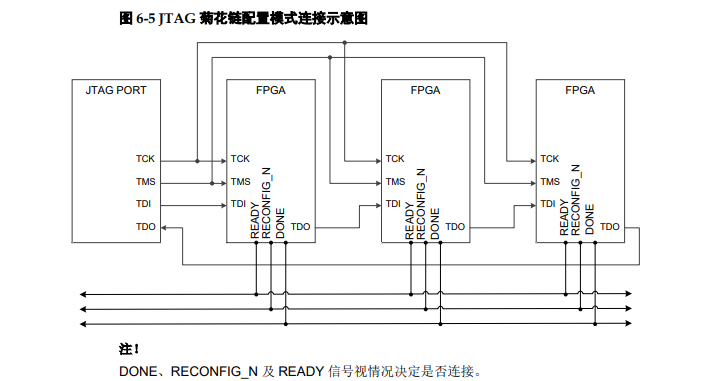

此外,高云半导体 FPGA 产品支持 JTAG 菊花链操作,即,把一个

FPGA 的 TDO 管脚连接到下一个 FPGA 的 TDI 管脚,Gowin 编程软件会自动识别连接在一起的 FPGA 器件,依次进行配置。菊花链配置的连接示意图如图 6-5 所示。

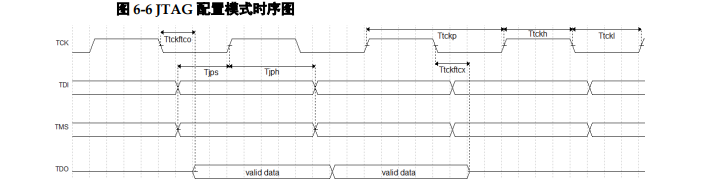

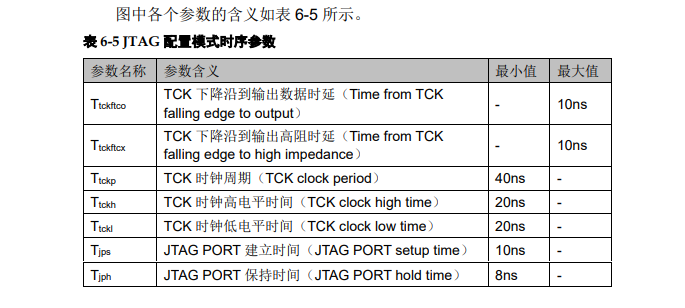

6.2.3 JTAG 配置模式时序图

JTAG 配置模式的时序图如图 6-6 所示。

6.2.4 JTAG 相关配置流程

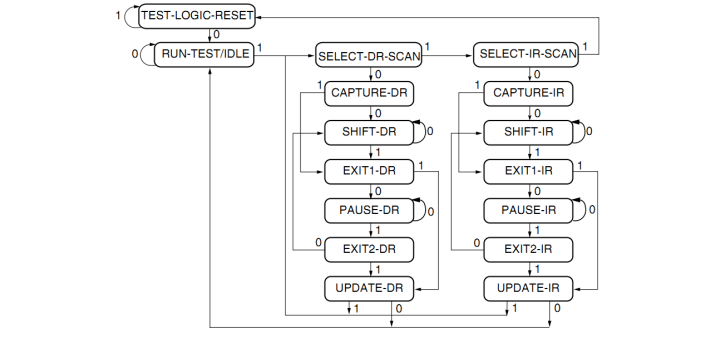

TAP 状态机

测试访问口状态机旨在选择指令寄存器或数据寄存器,使其连接至 TDI

和 TDO 之间。一般来说,指令寄存器用于选择需扫描的数据寄存器,在状态机框图中,位于箭头一侧的数字表示 TCK 变高时 TMS 的逻辑状态,如图所示。

图 6-7 TAP 状态机

TAP 复位

通过保持 TMS 为高电平(逻辑“1”)并在 TCK 端输入至少 5 个选通脉冲(变高后再变低)后,复位 TAP 逻辑,从而实现将处于其它状态的

TAP 状态机转换成测试逻辑复位状态,对 JTAG 接口和测试逻辑复位。

注!

该状态不复位 CPU 和外设。

注!

在进入 Shift_DR 或 Shift_IR 状态时,TDO 上的数据从 TCK 的下降沿开始有效;

在进入 Shift_DR 或 Shift_IR 状态时,数据不移位;

在离开 Shift_DR 或 Shift_IR 时,数据被移位;

最先移出的是数据的最低位 LSB;

一旦复位,所有指令将被重置或失效。

指令寄存器和数据寄存器

除测试逻辑复位外,状态机亦可控制两个基本操作:

指令寄存器(IR)扫描;

数据寄存器(DR)扫描。

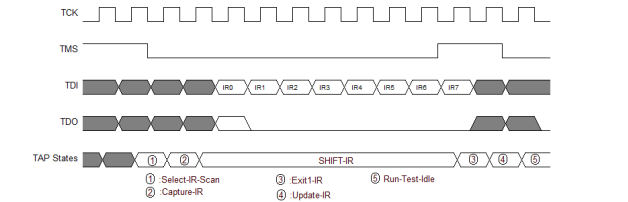

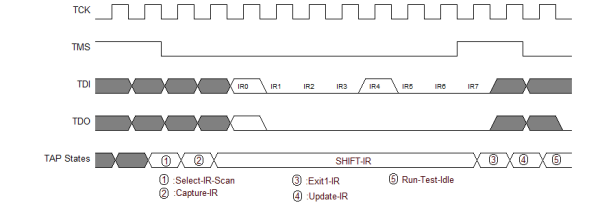

在指令寄存器扫描操作中,在 Shift_IR 状态时,传送数据或指令给指令寄存器,发送时采用 LSB 的方式,低数据位首先被发送,回到 Run-TestIdle后指令即被发送完毕,如图 6-8 所示。

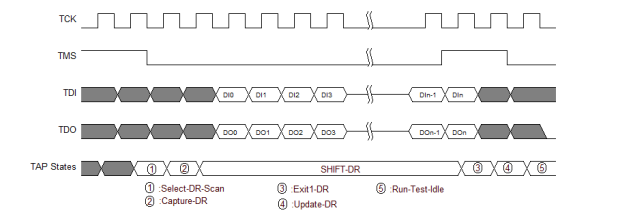

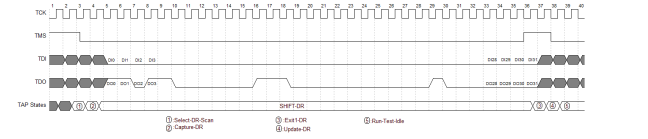

在数据寄存器扫描操作中,在 Shift_DR 状态时,传送数据或指令给数据寄存器,如图 6-9 所示。数据发送采用 LSB 还是 MSB 取决于具体操作。

图 6-8 指令寄存器访问时序

图 6-9 数据寄存器访问时序

注!

在高云半导体 GW1N(R)、GW2A(R)系列 FPGA 中,指令寄存器的总长度为 8 位;

根据所选择的寄存器,数据寄存器的长度可变化。

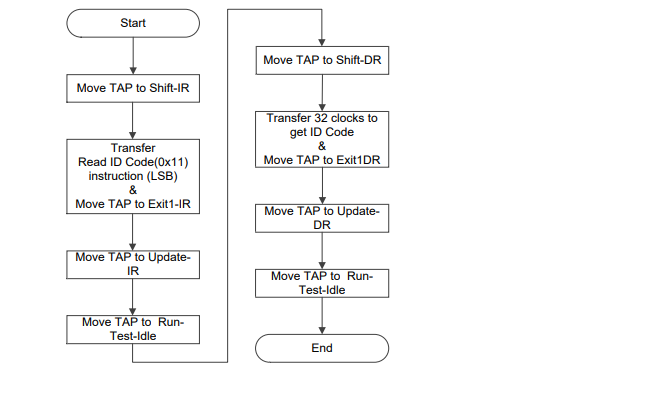

读取 ID CODE 实例

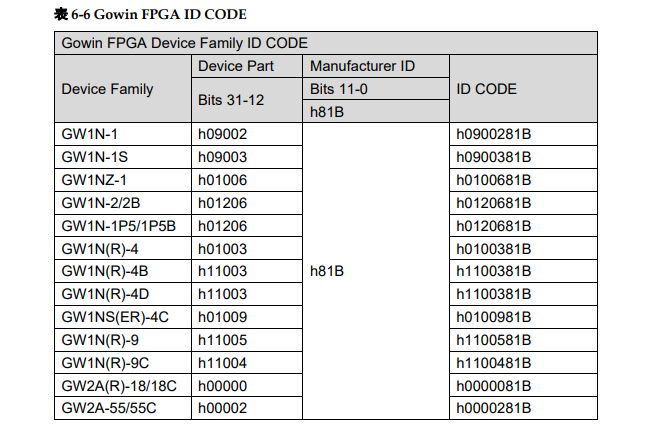

ID Code 即 JEDEC ID Code,是 FPGA 器件的一个基本标识。

高云 FPGA ID Code 长度为 32 位,下表列出了高云部分 FPGA 的 ID Code。

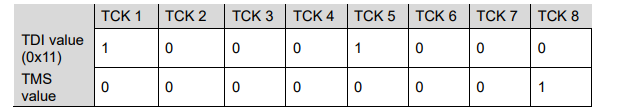

读取 FPGA 的指令是 0x11,以下步骤以读取 GW1N-4 ID Code 为例说明 JTAG 的工作方式。

1. TAP 复位:TMS 置为高电平,连续发送至少 5 个时钟周期;

2. 移动状态机从 Test-Logic-Reset 到 Run-Test-Idle;

3. 移动状态机到 Shift-IR,从最低位开始发送 Read ID 指令 0x11,最高位(最后一位)发送的同时移动状态机到 Exit1-IR,即最高位发送前

TMS 要置于高电平,表 6-7 给出 8 个时钟周期内发送 0x11 过程中 TDI

和 TMS 的值变化,时序如图 6-11 所示。

表 6-7 发送指令过程中 TDI 和 TMS 的值变化

4. 移动状态机,从 Exit1-IR 经过 Update-IR 后回到 Run-Test-Idle,并在

Run-Test-Idle 运行至少 3 个时钟周期;

5. 移动状态机到 Shift-DR,发送 32 个时钟周期,并在第 32 个时钟发送前,置 TMS 为高电平,完成 32 个时钟周期的同时,跳出 Shift-DR 到

Exit1-DR。这期间,发送 32 个时钟即可读出 32bits 数据,即为

0x0100381B,如图 6-12 所示;

6. 移动状态回到 Run-Test-Idle。

图 6-10 读取 ID Code 状态机流程图

图 6-11 读取 ID Code 指令-0x11 访问时序

图 6-12 读取 ID Code 数据寄存器访问时序

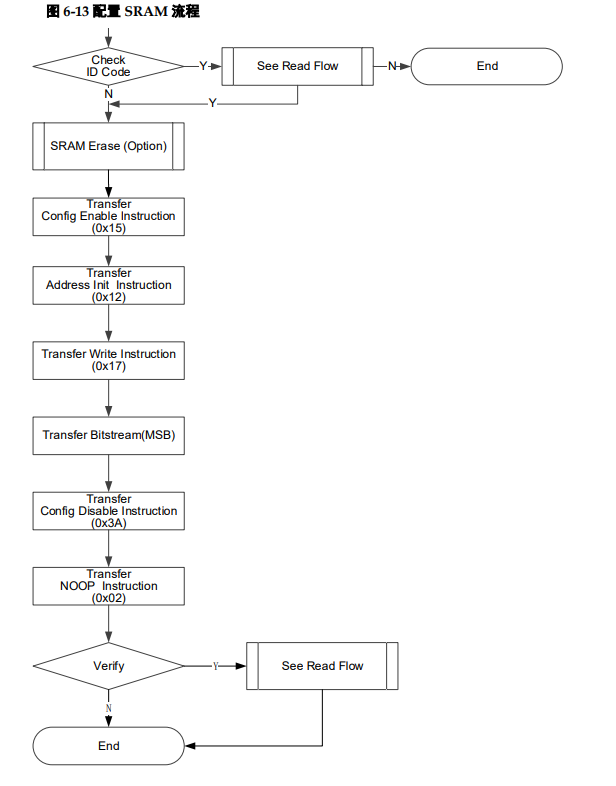

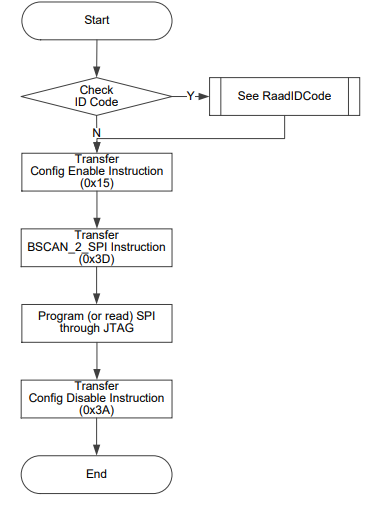

配置 SRAM 的流程

通过外部 Host 配置 FPGA SRAM,使 FPGA 实现功能,通过 JTAG 配

置 SRAM 不受 Configration Mode Pins 的影响。

通过 Gowin software 设计软件生成数据流文件,利用 JTAG 实现

SRAM 的配置,下面介绍外部 Host 配置 SRAM 的过程,如图 6-13 所示。

1. 建立 JTAG 链路,TAP 复位;

2. 读取设备 ID CODE,检查 ID CODE 是否匹配;

3. 如 SRAM 已被配置,擦除 SRAM,流程参考“擦除 SRAM 的流程”;

4. 发送 ConfigEnable 指令 0x15。

5. 发送 Address Initialize 指令 0x12;

6. 发送 Transfer Configuration Data 指令 0x17。

7. 移动状态到 Shift-DR(数据寄存器),将 Bitstream Data 从最高位开始(MSB),逐位发送,发送全部数据流文件内容,并回到 Run-Test-Idle状态;

8. 发送 Config Disable 指令 0x3A;

9. 发送 Noop 指令 0x02,结束配置流程。

10. 如需回读 Configuration Data 进行校验,请参考“读取 SRAM 的流程”。

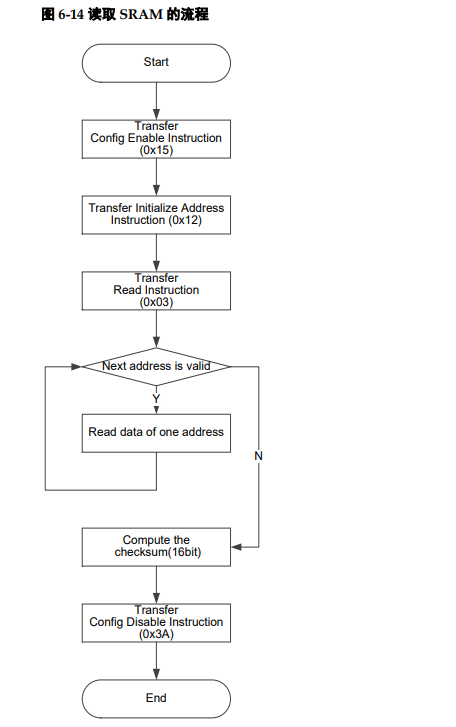

读取 SRAM 的流程

警告:处于数据保密设计,SRAM 数据默认不被允许回读。

从 FPGA 的 SRAM 区域读取 SRAM 数据,首先应保证写入 SRAM 时未配置安全位(Security Bit),安全位是用于保护运行时数据,保证数据安全。安全位完成设置后,从 SRAM 取回的数据均为 1(高电平)。

在加载过程中,FPGA 对写入数据进行 CRC 校验,以确保数据写入正确,CRC 是否报错,可以作为配置 SRAM 的校验机制。

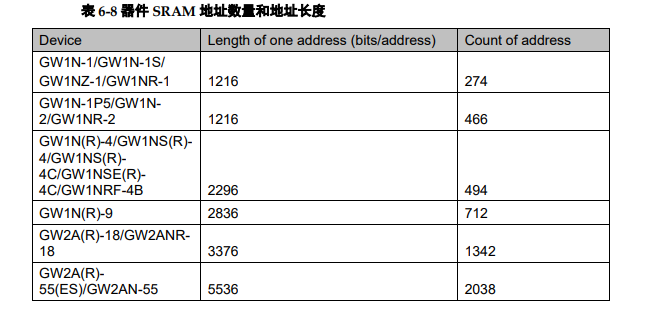

下面详细介绍读取流程,如图 6-14 所示。

1. 发送 ConfigEnable 指令 0x15;

2. 发送 Address Initialize 指令 0x12;

3. 发送 SRAM Read 指令 0x03;

4. 移动状态机到 Shift-DR(数据寄存器),发送地址长度数量的时钟,请参见表 6-8。在发送最后一个时钟同时拉高 TMS,跳到 Exit1-DR,此时 TDO 读取相应长度的数据。最后回到 Run-Test-Idle;

5. 重复步骤 4,每次读取一个地址的数据,其地址会自动累加;

6. 发送 Config Disable 指令 0x3A;

7. 发送 Noop 指令 0x02,结束读取流程。

擦除 SRAM 的流程

当重新配置 SRAM 时,需要擦除已存在的 SRAM。流程如下:

1. 发送 ConfigEnable 指令 0x15;

2. 发送 SRAM Erase 指令 0x05;

3. 发送 Noop 指令 0x02;

4. 延时或 Run Test 2~10ms;

5. 发送 SRAM Erase Done 指令 0x09;

6. 发送 Config Disable 指令 0x3A;

7. 发送 Noop 指令 0x02,结束流程;

注!

在发送 EraseSram(0x05)指令、Noop(0x02)之后,要给足够的时间等待其擦除完毕:

GW1N(*)-1 参考时间为 1ms;

GW1N(*)-4 参考时间为 2ms;

GW1N(*)-9 参考时间为 4ms;

GW2A(*)-18 参考时间为 6ms;

GW2A(*)-55 参考时间为 10ms。

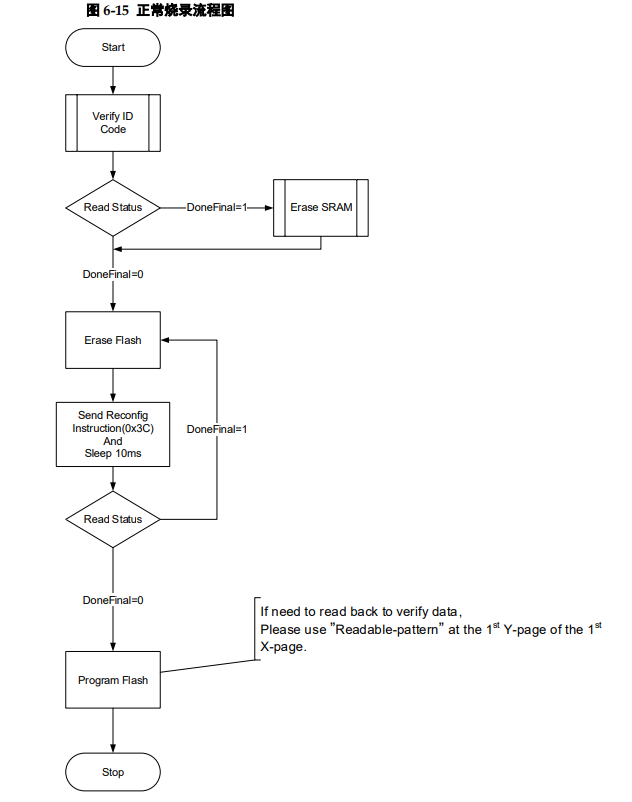

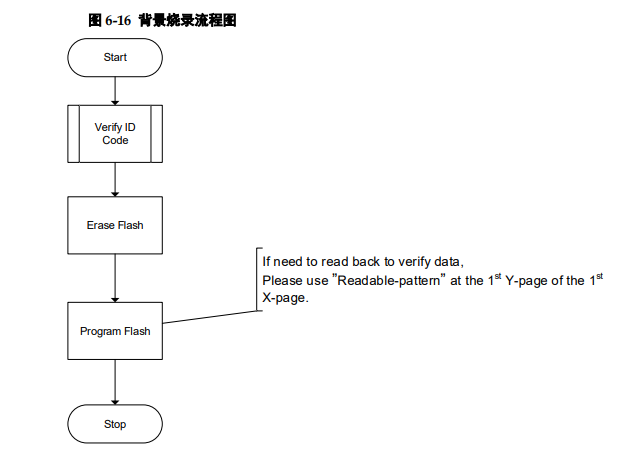

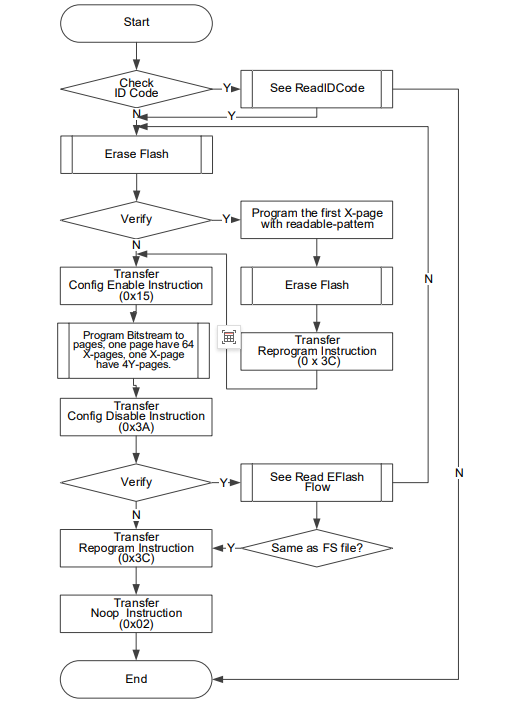

内置 Flash 烧录流程

烧录内置 Flash 分为正常烧录和背景烧录。两种配置的流程图如图 6-15

及图 6-16 所示。

擦除内部 Flash

高云 GW1N 系列内置 Flash 存储器,在每次编程之前需要先擦除内置

Flash,为保证数据安全,内置 Flash 只提供整片擦除的操作。

当前,内置 Flash 因工艺不同,对 JTAG 编程频率有不同要求,请参见表 6-9。

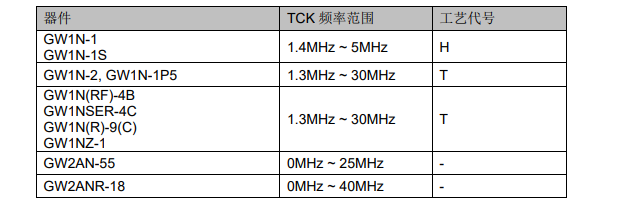

表 6-9 JTAG 的 TCK 频率要求

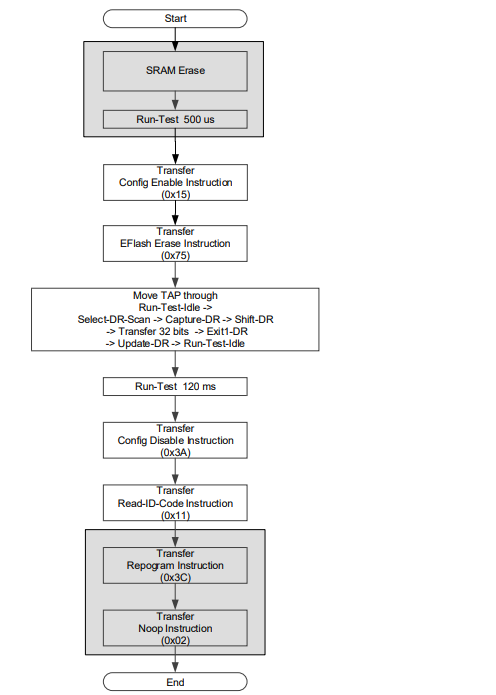

T 工艺系列 FPGA 擦除流程

下面详细介绍 T 工艺,GW1NZ-1 系列芯片的擦除流程(其他型号请忽略),如图 6-17 所示。

1. 建立 JTAG 链路,TAP 复位;

2. 读取设备 ID CODE,检查是否匹配;

3. 如果 SRAM 被配置过,先擦除 SRAM;

4. 在 Run-Test-Idle 持续产生时钟(Run-Test),持续时间为 500μs;

5. 发送 ConfigEnable 指令 0x15;

6. 发送 EFlash Erase 指令 0x75;

7. 依次移动状态机:Run-Test-ldle -> Select-DR-Scan -> Capture-DR ->

Shift-DR -> Transfer 32 bits-> Exit1-DR -> Update-DR -> Run-Test-ldle

(除 GW1N-4 系列外其他器件可忽略此步骤);

8. 在 Run-Test-Idle 持续产生时钟(Run-Test),持续时间为 120ms,此处有频率要求,见表 6-9;

9. 发送 Config Disable 指令 0x3A;

10. 发送 Noop 指令 0x02,擦除流程结束;

11. 发送 Reprogram 指令 0x03,使器件重配置,检查是否擦除成功。

图 6-17 擦除 T 工艺内部 Flash 擦除流程

注!

背景烧录时,忽略底纹区域操作

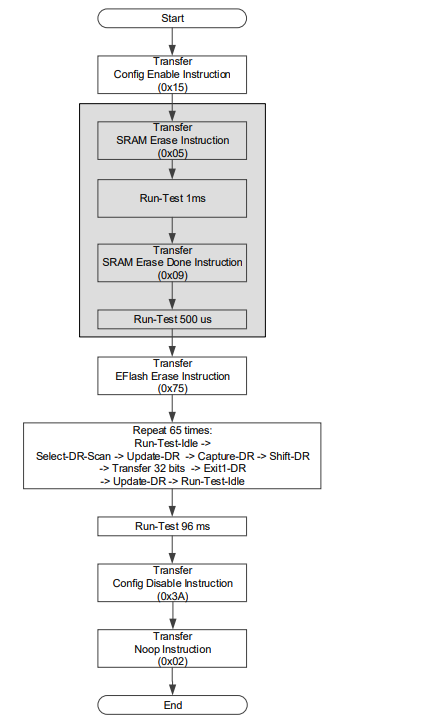

H 工艺 FPGA 擦除流程

H 工艺 FPGA 芯片的擦除流程:

1. 发送 ConfigEnable 指令 0x15;

2. 发送 EFlash Erase 指令 0x75;

3. 移动状态机,从 Run-Test-Idle 到 Shift-DR,产生 32 个时钟(TDI 信号保持低电平)。在第 32 个时钟同时移动状态机到 Exit1-DR,再经过Update-DR 回到 Run-Test-Idle;

4. 重复上述步骤,总共 65 次;

5. 在 Run-Test-Idle 持续产生时钟(Run-Test),持续时间为 95ms,此处有频率要求,见表 6-9;

6. 发送 Config Disable 指令 0x3A;

7. 发送 Repogram 指令 0x3C,检验是否擦除成功;

8. 发送 Noop 指令 0x02,擦除结束。

图 6-18 擦除 H 工艺 FPGA 内部 Flash 流程

编程内部 Flash 流程

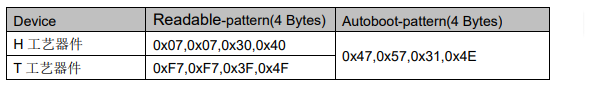

内置 Flash 以 256Bytes 为一个 X-page,每个 X-page 分成 64 个 Ypage,每Y-page 包含 4Bytes。

第一个 X-page 的第一个 Y-page,用于标识 Flash 是否可以具备

Autoboot(自动加载)功能或回读功能。如表 6-10 所示。当第一个 Y-page

写入 Readable-pattern 后,可读取 Flash 数据;当第一个 Y-page 写入

Autoboot-pattern 后,器件在 autoboot mode 下会自动把 Flash 数据加载到

SRAM 中;只有写入 Readable-pattern 后才能读取 Flash,其他情况均不能读取。具备 Backgroud programming 功能的器件,仅需使用 Autobootpattern。

在不需要回读数据的情况下,必须在数据流文件头部插入 Autobootpattern数据。当一个 X-Page 不足 256bytes 时,可使用 0xFF 或者 0x00

补齐。

当前,GW1N 系列内置 Flash 因工艺不同,对 JTAG 编程频率有不同要求,请参见擦除 SRAM 的流程>表 6-9 JTAG 的 TCK 频率要求。

表 6-10 Readback-pattern / Autoboot-pattern

编程内部 Flash 流程如图 6-19 所示:

1. 检查 ID Code 是否匹配;

2. 擦除内置 Flash;

3. 验证是否擦除成功,可通过读取 Status 寄存器,看器件是否已还原为裸片的初始状态,对背景烧录和 GW1NS 系列器件不能通过查看 Status来判断;

4. 发送 ConfigEnable 指令 0x15;

5. 以 X-page 为单位,每次写一个 X-page,直至烧录完成;

6. 发送 Config Disable 指令 0x3A;

7. 发送 Reprogram 指令 0x3C,使器件加载 Flash 的数据到 SRAM;

8. 读取 Status Code/User Code 验证是否加载成功。

图 6-19 编程内部 Flash 流程图

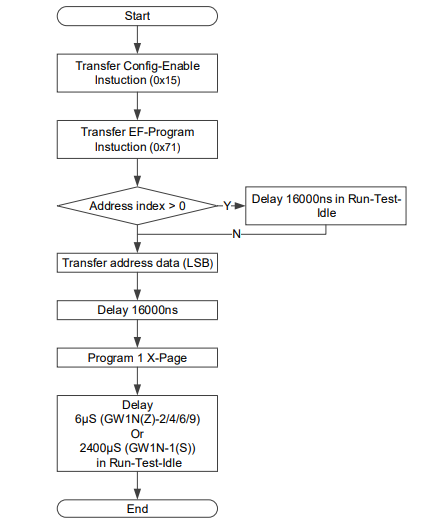

编程一个 X-page 流程

编程一个 X-page 流程如下描述,如图 6-20 所示。

1. 发送 ConfigEnable 指令 0x15;

2. 发送 EF-Program 指令 0x71;

3. 进入 Shift-DR 发送地址数据 1;

4. 写入一个 X-page 的数据。

一个 X-page 共 256 个字节,分 64 次,每次编程 4Bytes(即编程一个Y-page);Y-page 数据遵循 LSB 方式写入。此处流程可见图 6-20。

5. 写完一个 X-page 之后,GW1N-1(S)器件需要执行 2400μs 时长的时钟,GW1N(Z)-2/4/6/9 系列器件需要执行 6μs 时长的时钟,其他系列器件不需要额外时钟; 6. 本次 X-page 编程完毕。

注! [1]地址数据格式共 32bits,其中低 6 位保留,例如地址为 b’00010011(0x13)时,写入的地址为 b’ 00000000000000000000010011000000,该地址数据遵循 LSB 方式写入,最后一个 bit 跳出 Shift-DR。

图 6-20 X-page 编程流程图

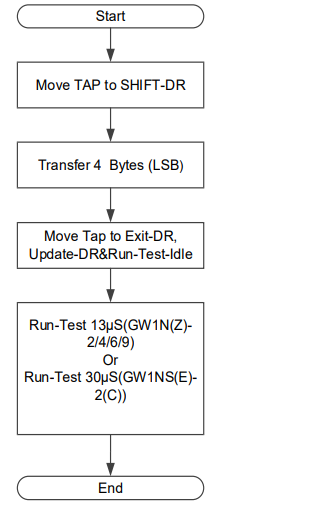

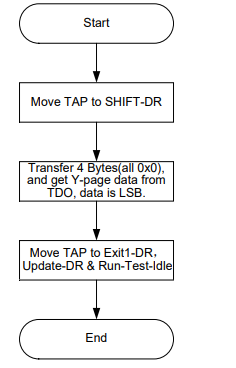

编程一个 Y-page 流程

Y-page 编程是烧录过程的最小单位,每次写入 4Bytes,数据写入遵循

LSB 方式写入,如图 6-21 所示。

写入完成,不同系列的器件都有要求执行 Run-Test 以等待写入完成,并且要 JTAG 时钟要满足最低频率要求,见表 6-9。

每次写完一个 Y-page, GW1N(Z)-2/4/6/9 系列要求 Run-Test 13-15μs,

GW1N-2(C)系列要求 Run-Test 30-35μs,其他系列器件不需要。

注!

数据从 Configuration Data 取高位 4Bytes,在 Shift-DR 写数据时要从最低位开始写入(LSB)。

图 6-21 Y-page 编程流程图

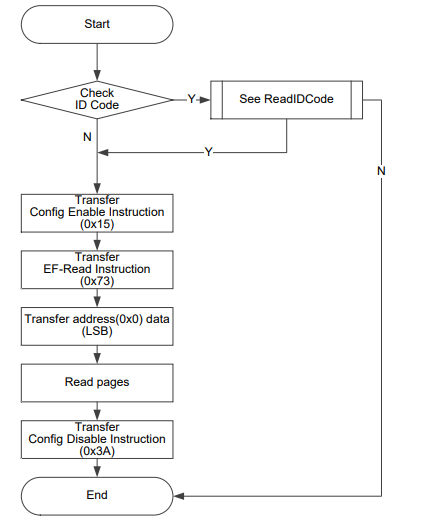

读取内部 Flash 流程

读取内部 Flash 流程概览,对 JTAG 的 TCK 没有速率要求。如图 6-22

所示。

读取内部 Flash 可以理解为是烧录 flash 的逆向过程,但首先要确保写入的 Readable-pattern 已经生效。对于 GW1N 而言,写入 Readablepattern后依次发送 Reprogram(0x3C)和 Noop(0x02)可使内部 flash 处于Readable 状态。

流程简述:

1. 校验 IDCode(可选);

2. 发送 ConfigEnable 指令 0x15;

3. 发送 EF-Read 指令 0x73;

4. 发送读 Flash 起始地址 0x0;方法同 0 中写 X-address 相同;

5. 每读 64 个 Y-page 就是一个 X-page;

6. 每次读完一个 X-page 并不需要重新发送地址,其地址会自动递归;

7. 读取完毕后,发送 ConfigDisbled 指令 0x3A 结束流程。

图 6-22 读取内部 Flash 流程图

读取一个 Page(Y-page)的过程

与写一个 Y-page 相似,但无写入 Flash 的等待时间,如图 6-23 所示。

数据最先输出的是数据最低位。

图 6-23 读取一个 Y-page 的过程

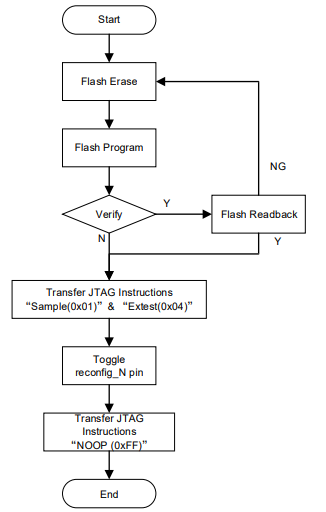

背景烧录(Background Programming)

设备有时需要在不影响当前功能的情况下升级数据文件,对 Flash 进行烧录。并且在加载新的数据流文件时,能够保持 IO 状态。下图是 GW1N-4

使用背景烧录技术(Background Programming)升级内置 Flash 数据的流程示意图。

图 6-24 GW1N-4 背景烧录流程图

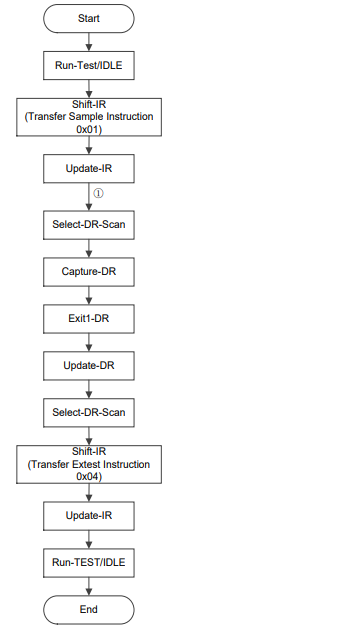

Transfer JTAG Instructions Sample & Extest 流程图如图 6-25 所示。

图 6-25 Transfer JTAG Instruction Sample & Extest 流程图

注!

○1 处直接从 Update-IR 跳入 Select-DR-Scan。

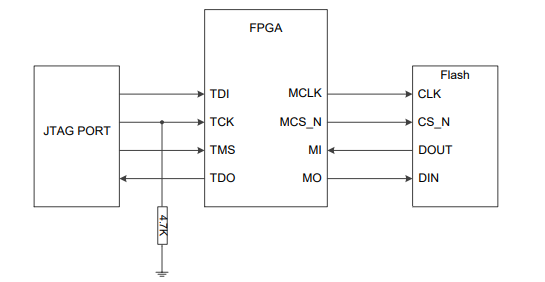

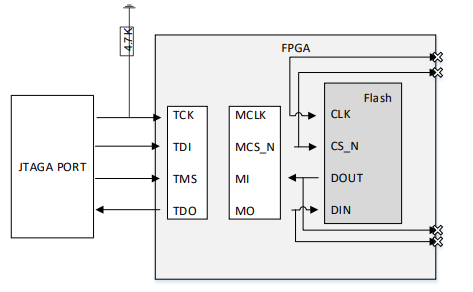

编程外部 Flash 或内嵌 SPI-Flash

高云 FPGA 可从外部 Flash 中加载数据流文件,可以通过 JTAG 直接烧录外部 Flash。

注! GW2AN-55 内部封了一颗 SPI-Flash,编程方式与 GW2A-18、GW2A-55 相同,GW2AN55外部的 MCLK,MCS_N,MI,MO 四个管脚必须悬空。

图 6-26 JTAG 接口编程外部 Flash 连接示意图(GW2A-18/GW2A-55 /GW1N)

注!

此图为 JTAG 接口编程外部 Flash 的最小系统图。

图 6-27 JTAG 接口编程内部 SPI-Flash 连接示意图(GW2AN-55)

注!

此图为 JTAG 接口编程内嵌 SPI-Flash 的最小系统图,MSPI 的四个管脚要悬空。

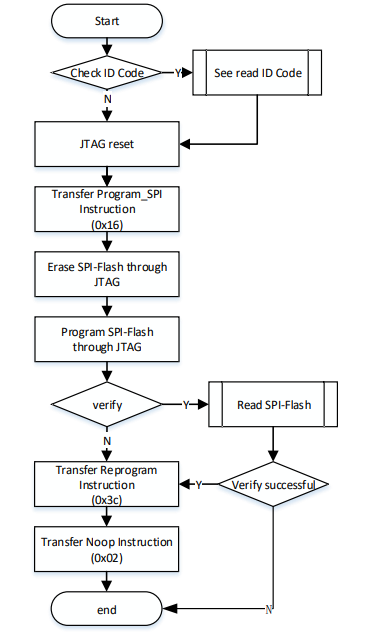

JTAG 转换 SPI 烧录外部 Flash

此模式通过 JTAG 接口编程外部 Flash。

此模式的原理是将 JTAG 的接口以转发的形式接入 Flash 的接口,用户通过 JTAG 模拟 Master SPI 时序对 SPI Flash 进行编程。

注!

发送 0x16 之后,FPGA 将 JTAG 信号转发至 MSPI 管脚,以配置 SPI-Flash; 当

JTAG 复位时该转发功能失效。

当从 SPI-Flash 回读数据时,第一个时钟数据为无效数据。如:回读 Flash ID code,发完 0x9F 指令后需要多发一个 clock 再回读 3Byte 数据。

JTAG 需要在 SHIFT-DR 状态下模拟 SPI 的时序。

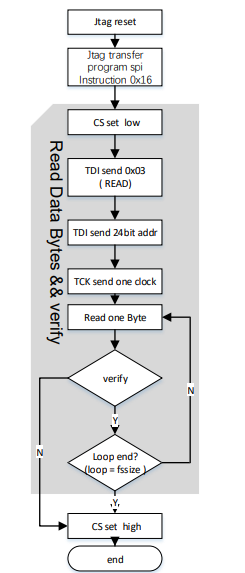

图 6-28 编程 SPI Flash 流程示意图

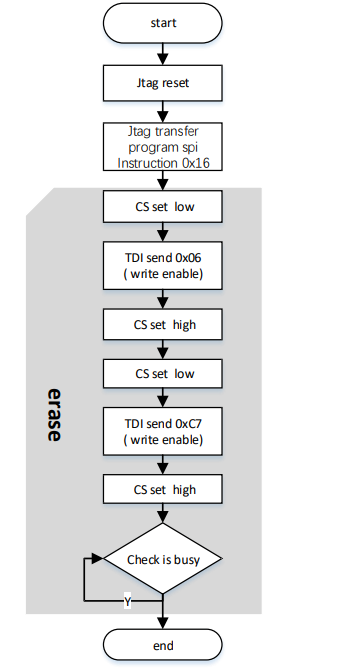

SPI-Flash 擦除流程图如图 6-29 所示:

图 6-29 擦除 SPI Flash 流程示意图

SPI-Flash 擦除流程:

1. JTAG 复位;

2. JTAG 转发 program spi Instruction 0x16 (LSB);

3. JTAG 的 TCK ,TMS, TDI, TDO 信号分别接到 MCLK ,CS,MOSI,MISO;

4. JTAG 控制 CS 拉低,控制 MOSI 写指令 0x06;

5. JTAG 控制 CS 拉高;

6. JTAG 控制 CS 拉低,控制 MOSI 写指令 0xc7;

7. JTAG 控制 CS 拉高;

8. 检查 SPI 是否 busy;

9. 擦除结束。

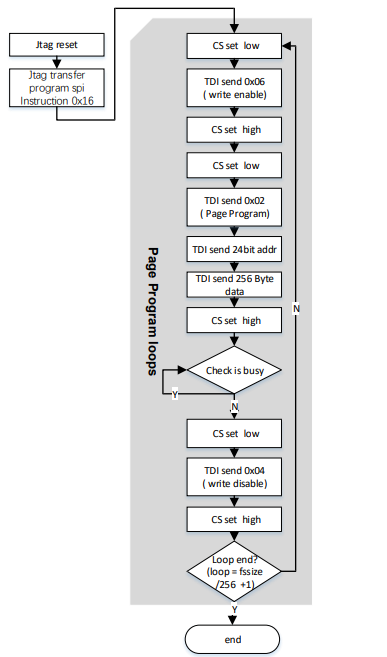

SPI-Flash 编程一个 page 流程,编程 SPI-Flash 以 page 为单位,循环编程:

图 6-30 SPI-Flash 编程一个 page 流程

SPI-Flash 编程一个 page 流程:

1. JTAG reset;

2. JTAG 转发 program spi Instruction 0x16 (LSB);

3. JTAG 的 TCK ,TMS, TDI, TDO 信号分别接到 MCLK ,CS,MOSI,MISO;

4. JTAG 控制 CS 拉低,控制 MOSI 写指令 0x06;

5. JTAG 控制 CS 拉高;

6. JTAG 控制 CS 拉低,控制 MOSI 写指令 0x02 和 3Byte 的地址和256Byte fs 数据;

7. JTAG 控制 CS 拉高;

8. 检查 SPI 是否 busy;

9. JTAG 控制 CS 拉低,控制 MOSI 写指令 0x04;

10. JTAG 控制 CS 拉高;

11. 写一个 page 结束。 SPI-Flash 回读并校验数据流文件流程图如图 6-31 所示:

图 6-31 SPI-Flash 回读并校验数据流文件流程图

SPI-Flash 回读并校验数据流文件流程:

1. JTAG reset;

2. JTAG 转发 program SPI Instruction 0x16 (LSB);

3. JTAG 的 TCK, TMS, TDI, TDO 信号分别接到 MCLK ,CS,MOSI,MISO;

4. JTAG 控制 CS 拉低,控制 MOSI 写指令 0x03 和 3Byte 的地址;

5. JTAG 控制 MCLK 发送一个 clock;

6. JTAG 回读数据,一次回读 1Byte;

7. 回读数据与写入的数据流文件进行比对,比对一致则继续比对下一 Byte

直到最后一个 Byte;如果不一致则跳出循环;

8. JTAG 控制 CS 拉高;

9. 回读校验结束。

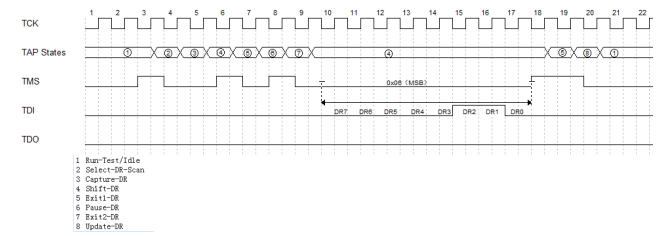

图 6-32 GW2A 系列 JTAG 模拟 SPI 发送 0x06 指令时序图

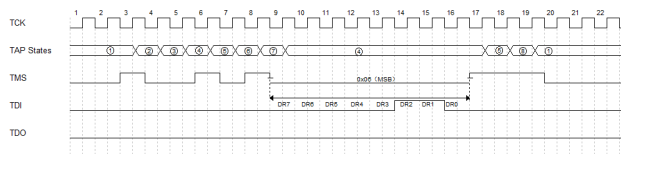

图 6-33 GW1N 系列 JTAG 模拟 SPI 发送 0x06 指令时序图

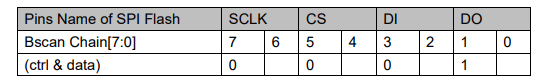

JTAG Boundary Scan 模式烧录 SPI Flash

该模式的原理,是使用 Boundary Scan 的方式改变与 SPI 相连管脚的状态来实现 SSPI 时序,从而编程内部 Flash。

该模式采用的 Boundary Scan Chain 长度为 8 位,每 2 位组合对应管脚的状态,如表 6-11 所示,每发送两次 Boundary Scan Chain 完成一次SCLK 驱动。

表 6-11 管脚状态

注!

ctrl:0 表示输出,1 表示输入;

data:0 表示低电平,1 表示高电平。

图 6-34 采用 Boundary Scan 模式编程 SPI Flash 流程示意图

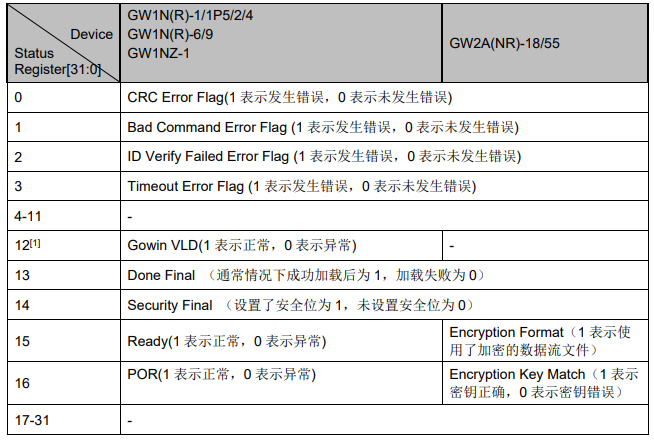

读取 Status Register 0x41

Status Register 在器件调试和观察器件状态有很大帮助,通过读取

Status Register,可初步判断器件的状态,如判断是否成功 wakeup、是否存在加载错误等。 Status Register 共有 32 位,读取指令是 0x41,时序与 Read ID Code

一致。 Status Register 的含义如表 6-12 所示。

表 6-12 Status Register 与配置加载相关的条目

注! [1] Gowin VLD 是内置 Flash 相关参数。

GW1N 家族 FPGA 器件编程

状态寄存器的 Bit-15 READY 仅在编程出错时返回 0x0。编程时出现的错误包括 CRC 错误、错误的命令、ID CODE 不匹配等。

如果状态寄存器 Bit-15 READY 返回 0x0,可通过检查状态寄存器

Bit[3:0]以确定下载错误的原因。

状态寄存器 Bit-13 DONE 必须始终结合 READY(见上文)来确认下载是否成功,无法单独使用。

GW1N 家族 FPGA 器件状态寄存器返回值

0x0001B020(安全位未置 1)表示 FPGA 已配置成功(不建议在生产中采用这种做法,因为这会导致可以从 SRAM 中读取下载数据)。 0x0001F020 (安全位置 1)亦表示 FPGA 已配置成功

即下载成功情况下的状态寄存器返回值为:

Bit-16 POR = 0x1

Bit-15 Ready = 0x1

Bit-14 Security Final = 0x1 或 0x0 (见上文)

Bit-13 DONE Final = 0x1

Bit-12 VLD = 0x1

GW2A 家族 FPGA 器件编程

当对 GW2A 器件进行编程时,以下位只在编程过程中使用,编程完成

后,这些位会被自动清零。也就是说,这两个位的最终状态返回值将始终为

0x0。

Bit-15 Encrypted Format

Bit-16 Encrypted Key is Right

此外,GOWIN VLD 状态位只适用于有内嵌 Flash 的设备。因此,

GW2A 家族器件的 Bit-12 也将返回 0x0。 GW2A 家族 FPGA 器件状态寄存器返回值

0x02020(安全位未置 1)表示 FPGA 已配置成功(不建议在生产中采用这种做法,因为这会导致可以从 SRAM 中读取下载数据)。 0x06020(安全位置 1)亦表示 FPGA 已配置成功。

即下载成功情况下的状态寄存器返回值为:

Bit-16 = 0x0

Bit-15 = 0x0

Bit-14 Security Final = 0x1 或 0x0 (见上文)

Bit-13 DONE Final = 0x1

Bit-12 = 0x0

读取 User Code 0x13

User Code 共有 32 位,读取指令是 0x13,时序与 Read ID Code 一致。 User Code 默认使用的是 FS 文件的 checksum 值,可在 Gowin Designer 中重新定义。

重加载 0x3C

该指令作用是使 FPGA 从 flash 中读取数据流文件,并配置到 SRAM。

通过 JTAG 依次发送 Reprogram(0x3C)指令、Noop(0x02)指令,可使器件重加载,效果同触发 Reconfig_N 管脚 。

菊花链连接示意图

图 6-35 菊花链连接示意图