文章目录

- 设计目标

- 硬件设计

- 数码管

- 串口

- 软件设计

- 顶层模块

- 串口接收模块

- 数据处理模块

- 时钟模块

- 串口发送模块

- 总结

设计目标

环境:ACX720开发板

实现功能:

- 数码管能够显示时分秒

- 能够接收串口数据修改时间

- 能够将当前时间以1s一次速率发送到电脑

硬件设计

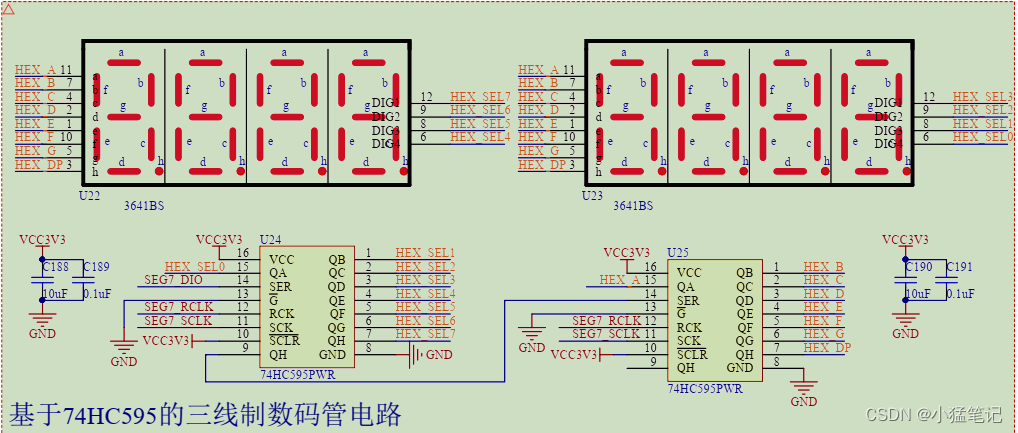

数码管

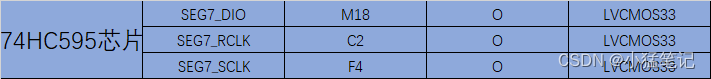

串转并芯片:74hc595:

两片级联,一片控制数码管的位选,一片控制段选。

使用的是共阳极数码管

两片级联一次发送16位数据,也就是2个字节。

芯片输入:

SER:DIO:数据输入引脚

RCK:RCLK:锁存引脚,上升沿对输入数据锁存输出

SCK:SCLK:移位引脚,将SER引脚数据输入,下降沿放数据,上升取数据并移位。

芯片在不同工作温度和工作电压下 74HC595 的芯片工作频率值不相同,本设计供电电压采用3.3V,并结合时钟频率,设置其工作频率为12.5MHz。

常见的显示设备有:

数码管:7段管、米字型、点阵

液晶屏:字符型(LCD1602、12864)、真彩液晶屏(TFT-LCD)

OLED

VGA、HDMI、DP显示器

串口

往期博文介绍:

https://blog.csdn.net/qq_30255657/article/details/132563322?csdn_share_tail=%7B%22type%22%3A%22blog%22%2C%22rType%22%3A%22article%22%2C%22rId%22%3A%22132563322%22%2C%22source%22%3A%22qq_30255657%22%7D

软件设计

顶层模块

串口接收—数据处理—时间设置、控制数码管显示时间、输出时间值

1s驱动—分析时间值并处理发送文章来源:https://uudwc.com/A/vm9wN

uart_rx_ctrl_lcd(

Clk,

Reset_n,

uart_rx,

Ds,

Sclk,

Rclk,

uart_tx

);

串口接收模块

uart_rx uart_rx_in(

.Clk(Clk),

.Reset_n(Reset_n),

.Baund_set(4),

.uart_Rx(uart_rx),

.Data(rx_data),

.Rx_Done(rx_done)

);

数据处理模块

uart_cmd uart_cmd(

.Clk(Clk),

.Reset_n(Reset_n),

.rx_data(rx_data),

.rx_done(rx_done),

.ctrl(ctrl),

.time_set(time_set)

);

时钟模块

shiZhong shiZhong1(

.Clk(Clk),

.Reset_n(Reset_n),

.Set_en(ctrl),

.Set_time(time_set),

.Ds(Ds),

.Sclk(Sclk),

.Rclk(Rclk),

.Out_time(Out_time)

);

串口发送模块

UART UART(

.Clk(Clk),

.Reset_n(Reset_n),

.Baud_set(3'd1),

.Data(data),

.Send_en(send_con),

.Tx_Done(Tx_Done),

.Tx_State(),

.uart_tx(uart_tx)

);

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

start <= 0;

else if(tcont == 1)begin

start <= 1;

state <= 0;

end

else if(tcont == 500000)

start <= 0;

else if(Tx_Done)

state <= state + 1;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

data <= 0;

else if(start)begin

case(state)

0:begin data = 8'h30 + Out_time[23:20]; send_con <= 1;end

1:data = 8'h30 + Out_time[19:16];

2:data = 8'h3a;

3:data = 8'h30 + Out_time[15:12];

4:data = 8'h30 + Out_time[11:8];

5:data = 8'h3a;

6:data = 8'h30 + Out_time[7:4];

7:data = 8'h30 + Out_time[3:0];

8:data = 8'h0d;

9:data = 8'h0a;

default:begin send_con <= 0; end

endcase

end

总结

规划好每一根信号线的时序再写,每个部分一个信号,不能多个部分驱动一个信号。文章来源地址https://uudwc.com/A/vm9wN